Introduction au VHDL

Introduction au VHDL

Introduction au VHDL

Préambule :

VHDLHDL HDL

!

VHDL"#

1. Introduction

VHDL#

!$CPLD

C!PLD#FPGAFP

GA%

&CPLDFPGA)'#

micro-contrôleurmicro-contrôleur figée,!

ROM RAM"#

(#C, ADA, Pascal, JAVA...#Assembleur

ROM!

&

'déconnectées les unes des autres#

schémaVerilog, VHDL

#structure logique souhaitée

micro-contrôleur)

circuit programmable

SFO 3MIC *+**

Introduction au VHDL

,""

-

VHDL##.

!%VHDL-

–Les descriptions VHDL synthétisables : #"%("

$%

#

–Les descriptions VHDL non synthétisables : #

%(%$

' ! # '

#%(#

#!

"

SFO 3MIC /+**

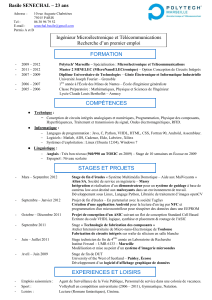

Schéma+0VHDL

1%("

1+

2

!

FPGACPLD

!

JAVA/ADA/C/Assembleur

1+

1

2

ROM ou RAM

Micro-contrôleur

Fig. 1 : comparaison des conceptions pour processeur et

pour circuit logique programmable

Introduction au VHDL

2. Structure d'un fichier VHDL

&( VHDL !"

Entity 34

%!

Exemple-

3. Structuration d'une architecture, process

&('#5

1('

VHDL#1 process

VHDL0#

( durée

d'exécution nulle !VHDL

SFO 3MIC 6+**

Valeurs d'un std_logic :

U' – Uninitialized

'X' – Forcing Unknown

'1' – Forcing 1

'0' – Forcing 0

Z' – High impedance

7879&9

:879*

879;

110

) # 6

%%

std_logicstd_logic_vector

)

;*-

((VHDL

-

Introduction au VHDL

##"&#(

$1

<signal (

0#((

"#-

0 ! =* =/ =

62=6#

#! '

$concurrents(>!

#

SFO 3MIC +**

=*

=/ =6

=

=">

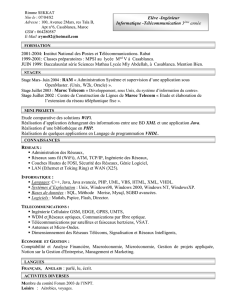

3!

%)

3!

%.&5

3%) .&5

<(<(

?

2@

@

2AB

liste de

se n si bi li té

2@

@

2AB

2@

@

2AB

$CD<< 0?AB

(B

Architecture VHDL

<

?

$

Fig. 2 : Association process – structure logique

Introduction au VHDL

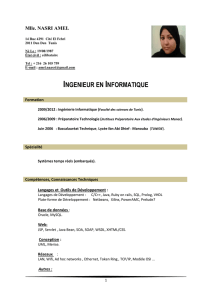

2!%"(

-

0"HRAZ#Q_int#2

E

F##Q_int

0"(

!%Q_int1##Q_int

"

2!-

Q_int = Q_int+1;

Q_int = Q_int+1;

Q_int = Q_int+1;

<#Q_intD/Q_int #6

GFQint "HI

"Q_int

(

if then else (#else$effet mémoire

# H Q_int & )J&K 5%

(#"Q_int(.

effet mémoire par omission ) #

#(

F

SFO 3MIC G+**

. !

$

Q_int #(Q

! 5

!!

⇒##H RAZ

⇒UP_DOWN(

# 0 #

NB: L'entrée d'un circuit logique ne fait pas

forcément partie de la liste de sensibilité, loin de là.

RAZ%asynchrone"

( ;

Q_int (

Process 1

Process 2

6

6

7

7

8

8

9

9

10

10

11

11

1

/

11

100%