Architecture du Pentium

1

©Pierre Marchand, 2001 24

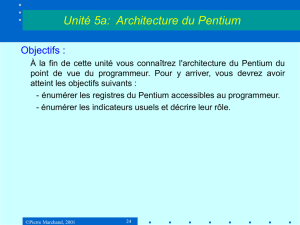

Objectifs :

À la fin de cette unité vous connaîtrez l'architecture du Pentium du

point de vue du programmeur. Pour y arriver, vous devrez avoir

atteint les objectifs suivants :

- énumérer les registres du Pentium accessibles au programmeur.

- énumérer les indicateurs usuels et décrire leur rôle.

Unité 5a: Architecture du Pentium

©Pierre Marchand, 2001 25

Pourquoi l’assembleur ?

• Rapide

• Compact

• Puissant

• Pour mieux comprendre et utiliser :

• les langages de haut niveau :

- variables globales

- variables locales et allocation dynamique

- passage de paramètres et variables registres

- déboguage

Unité 5a: Architecture du Pentium

2

©Pierre Marchand, 2001 26

Pourquoi l’assembleur ?

• Pour mieux comprendre et utiliser :

• les compilateurs :

- édition de liens

- génération de code

• La structure interne des processeurs

• La virgule flottante

• Les interruptions

• Pour mieux accéder aux périphériques

Unité 5a: Architecture du Pentium

©Pierre Marchand, 2001 27

Pourquoi l’assembleur ?

• Universellement utilisé

• Indispensable dans la programmation des microcontrôleurs ou des

systèmes embarqués

• Finalement, parce que c’est amusant!!

Unité 5a: Architecture du Pentium

3

©Pierre Marchand, 2001 28

Inconvénients de l’assembleur ?

• Plus long à programmer que les langages de haut niveau

• Pas de vérification de types

• Pas de structures de contrôle (if, while, etc.)

• Dépend du processeur

Unité 5a: Architecture du Pentium

©Pierre Marchand, 2001 29

Architecture de von Neumann

Unité 5a: Architecture du Pentium

0

n

F

816

PC

R1

R2

R3

R4

R5

Acc1

Acc2

Tampon

Tampon

ALU

Décaleur

S

S0

1

F

Décodeur

Micropro-

gramme

IR

Tampon

L0L1Verrou Verrou

BUS DE DONNÉES

CCR

BUS DE CONTRÔLE

BUS D'ADRESSES

4

©Pierre Marchand, 2001 30

Architecture de von Neumann

Exécution séquentielle des instructions

• Chargement (fetch) de l’instruction dans IR

• Décodage de l’instruction

• Chargement des opérandes s’il y a lieu

• Exécution

• Écriture du résultat

Même avec une horloge de 500 MHz,

un tel processeur serait plus lent que

les processeurs d’aujourd’hui.

Pourquoi ?

Unité 5a: Architecture du Pentium

0

n

F

816

PC

R1

R2

R3

R4

R5

Acc1

Acc2

Tampon

Tampon

ALU

Décaleur

S

S0

1

F

Décodeur

Micropro-

gramme

IR

Tampon

L0L1

Verrou Verrou

CCR

©Pierre Marchand, 2001 31

Architecture de von Neumann

• Les registres n’ont que 8 bits

• Bus d’adresses de 16 bits -> 64 Ko max de RAM

• Même si on mettait tous les registres à 32 bits et des bus de

données et d’adresses de 32 bits, on n’aurait pas encore une

performance élevée.

• Les accès mémoire prennent de l’ordre de 100 ns. Le processeur a

un temps de cycle de 2 ns à 500 MHz.

•Il faudrait donc ajouter un cache de niveau 1 sur la puce et un cache

de niveau 2.

• Il manque encore la virgule flottante et la mémoire virtuelle.

Unité 5a: Architecture du Pentium

5

©Pierre Marchand, 2001 32

Architecture de von Neumann

• Même en ajoutant des instructions de virgule flottante et la mémoire

virtuelle, on n’aurait pas encore une performance comparable à celle

des processeurs actuels.

•En effet, il n’y a qu’une unité d’exécution. Chaque instruction prend

au moins quatre à six cycles :

- Chargement de l’instruction

- Décodage de l’instruction

- Exécution de l’instruction

- Écriture du résultat.

• Et, le cas échéant,

- Chargement d’un ou deux opérandes

Unité 5a: Architecture du Pentium

©Pierre Marchand, 2001 33

Architecture de von Neumann

Or les processeurs actuels effectuent en moyenne plus d’une

instruction par cycle.

Comment y parviennent-ils ?

Unité 5a: Architecture du Pentium

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

1

/

19

100%