06-CMOS - La page perso de philippe laporte

Page : 1

Technologie - C MOS

Dans cette partie nous allons étudier la construction du C MOS ou Complementary MOS qui est un

assemblage technologique permettant de réaliser sur un même substrat des transistors N MOS et des

transistors P MOS.

Pour assembler ces deux types de transistors, il est nécessaire de créer une zone Si de type N dans le

substrat Si de type P : Le caisson.

Ph.LAPORTE

Élaboration des Circuits Intégrés

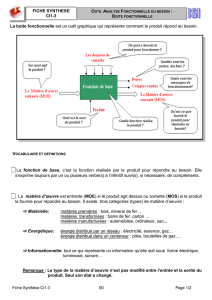

Qu'est-ce qu'un assemblage C MOS ?

C MOS (Complementary MOS)

=

assemblage technologique permettant de réaliser sur

un même substrat des transistors N MOS et P MOS

N+

Si N

Si P

N+ P+ P+

Caisson

NECESSITE DE CREER Un CAISSON

Page : 2

Technologie - C MOS

Pour réaliser un caisson N dans un substrat P, on procède par dopage localisé au phosphore de la zone du

caisson.

Au cours du recuit, le dopant est activé et diffuse pour former le caisson N.

Ph.LAPORTE

Élaboration des Circuits Intégrés

Comment créer un caisson ?

•A partir d'un substrat silicium de type P

•Dopage de la zone du caisson

(photolithographie + dopage Phosphore)

•Retrait résine,

•activation et diffusion du dopant

P

résine

Si P

Si P

Si P

Caisson Si N

Page : 3

Technologie - C MOS

Ce transparent résume les différences entre la séquence technologique du N MOS et celle du P MOS. Il

reprend le transparent vu précédemment, en y ajoutant le caisson.

Ces différences se situent au niveau :

• Du substrat sur lequel est construit le transistor :

Si P pour le N MOS

Caisson Si N pour le P MOS

• Du transistor : canal, source et drain

Les autres étapes restent identiques et peuvent donc être réalisées en même temps pour les deux types de

transistor.

Ph.LAPORTE

Élaboration des Circuits Intégrés

Comparaison entre les transistors

N MOS et P MOS - Technologie

Transistor

P MOS

Passivation finale

Métallisation

Contact

Protection du transistor

INTERCONNEXIONS

Type P

Type N

Type N

Transistor

N MOS

Type N

Type P

Type P

Source et Drain

Grille isolée

Canal

TRANSISTOR

Implantation de champ

Zone active

Caisson

Substrat

ISOLATION

En technologie C MOS :

•Réalisation des étapes identiques en même temps

•Dédoublement des étapes différentes

Page : 4

Technologie - C MOS

Les transparents qui suivent présentent comme nous l'avons fait pour le transistor N MOS, la réalisation

de l'isolation latérale :

• définition de la zone caisson

• formation du caisson par implantation

• définition des zones de LOCOS

• formation des zones de LOCOS par dopage aux bore

• croissance du LOCOS.

Ph.LAPORTE

Élaboration des Circuits Intégrés

La réalisation de l'isolation - 1

•A partir d'un substrat P

•Croissance d'un oxyde de protection

(oxydation) 40nm - 400Å

•Dépôt d'une couche de résine photosensible

Si P

Si P

Si P

Page : 5

Technologie - C MOS

Ph.LAPORTE

Élaboration des Circuits Intégrés

La réalisation de l'isolation - 2

•Définition de la zone du caisson

(photolithographie)

•Implantation phosphore

(environ 10e12 atomes/cm²)

•Formation du caisson :

retrait résine

désoxydation

recuit caisson légèrement oxydant

(environ 20nm - 200Å d'oxyde à 1150°C

pendant 30mn à qq heures)

Si P

Phosphore

Si P Si N

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

1

/

17

100%