poly-2-consommation de puissance Fichier

3A EMS

Energie pour les systèmes nomades 1

1

Consommation de puissance

(cours énergie pour les systèmes nomades)

Matthieu Denoual

ENSICAEN

2

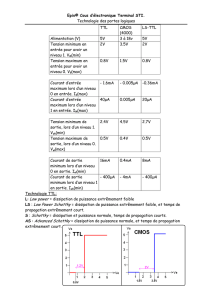

Préalable : rappel transistor MOS

Transistor NMOS

oxyde de grille

grille

drain

source

substrat

(bulk)

substrat

polysilicium de grille

3A EMS

Energie pour les systèmes nomades 2

3

Préalable : rappel transistor MOS

VDS=0.1VVGS0V

formation d’une région appauvrie

(depletion region)

pas de courant, car pas de porteurs de charge

transistor bloqué

4

Préalable : rappel transistor MOS

VDS=0.1VVGS0V

formation d’une couche d’inversion

(inversion layer)

le transistor devient passant

la valeur de VGS pour laquelle cela

a lieu est la tension de seuil VTH0

ox

dep

FMSTH C

Q

V

2

0

3A EMS

Energie pour les systèmes nomades 3

5

Préalable : rappel transistor MOS

effet de polarisation du substrat

FSBFTHTH VγVV

22

0

VDS=0.1V

VGS0V VDS=0.1V

VGS0V

VB<0VVSB=0V

γ

coefficient d’effet de polarisation du

substrat (0.3 à 0.4 V0.5)

VSB>0V

VSB=0V

6

Préalable : rappel transistor MOS

NMOS

PMOS

modèle électrique modèle logique

3A EMS

Energie pour les systèmes nomades 4

7

Préalable : flot de conception de circuit intégré

transistors

MOS

PMOS

NMOS

portes

logique

(CMOS)

composants

élémentaires

…

…

…

8

Préalable : flot de conception de circuit intégré

niveau algorithmique

synthèse architecturale

niveau architectural

synthèse logique

niveau logique

synthèse physique

niveau physique

niveau topologique

synthèse des masques

raffinement de la spécification

abstraction des paramètres physiques

librairie de

composants

librairie

de portes

librairie de

transistors

librairie de

masques

Z=X+Y

+

3A EMS

Energie pour les systèmes nomades 5

9

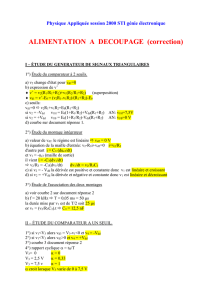

La problématique de la dissipation de puissance

Pourquoi doit-on considérer la dissipation de puissance ?

Puissance moyenne et pic

Poids/volume des batteries pour les applications portables

Défaillances dues à la température

Label faible-consommation, aspect écologique

Coût du packaging et système de refroidissement

Répartition de la puissance

dans un PC de bureau

Core i7 quad 110 W pleine charge

ARM Cortex A8 (iphone) 300 MHz, 1,25 W

Pentium III power density (W/cm²)> hotplate

10

La problématique de la dissipation de puissance

Pourquoi est-ce un enjeu réel aujourd’hui ?

Intégration : milliards de transistors

Vitesse, fréquence : GHz

Limites du Deep-submicron : la réduction de la tension d’alimentation n’est

plus une solution

Applications portables : tablette, 3/4G communications...

Besoin de plus de puissance

Plus de puissance dissipée

Réduire la dissipation de

puissance lors de la conception

Traiter les conséquences de

la dissipation de puissance

Techniques de réduction de la

consommation

Nécessaire de connaître les sources de

dissipation de puissance

Refroidissement

Récupération d’énergie

leakagenbtrfreqfP ,,,

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

1

/

17

100%