5 Codage EN VHDL

Projet de VHDL – un mini-processeur

- 1 -

UN MINI-PROCESSEUR

Projet de VHDL

Gregory Heinrich/Maël Le Berre

Historique du document

Version

Date

Modification

V0.01

26.10.2002

Document de référence initial

V0.02

29.10.2002

Addition d’informations sur l’architecture et définition des

entités

V0.03

10.11.2002

Addition des codes source et chronogrammes de simulation

V1.01

12.11.2002

Document rendu

Projet de VHDL – un mini-processeur

- 2 -

TABLE DES MATIERES

UN MINI-PROCESSEUR ...................................................................................... 1

TABLE DES MATIERES ............................................................................................................... 2

CONTEXTE ..................................................................................................................................... 4

1 OBJECTIFS ............................................................................................................................... 5

1.1 UN CODE REUTILISABLE ET COMMENTE ................................................................................. 5

1.2 UN CODE MODULAIRE POUR FACILITER LE TRAVAIL EN EQUIPE ............................................. 5

1.3 L’AVANTAGE DE L’OUTIL INFORMATIQUE ............................................................................. 5

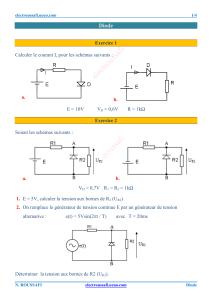

2 CAHIER DES CHARGES ....................................................................................................... 6

3 METHODOLOGIE POUR LE CODAGE EN VHDL ....................................................... 10

3.1 NOMENCLATURE DES SYMBOLES ......................................................................................... 10

3.1.1 Noms de fichiers ........................................................................................................... 10

3.1.2 Noms de types et de signaux ........................................................................................ 10

3.2 TYPES DE DONNEES UTILISES ............................................................................................... 10

Fichier upp_util_types.vhdl.conf ............................................................................................... 11

3.3 PACKAGES ........................................................................................................................... 13

Fichier upp_util_tools.vhdl ....................................................................................................... 13

4 ARCHITECTURE DU COMPOSANT ................................................................................ 14

4.1 L’UNITE ARITHMETIQUE ET LOGIQUE (UPP_ALU) ................................................................. 14

4.2 LE DECODEUR D’INSTRUCTIONS (UPP_DECODER) ................................................................ 15

4.3 LE PILOTE DE REGISTRES (UPP_REGDRIVER) ........................................................................ 15

5 CODAGE EN VHDL .............................................................................................................. 17

Projet de VHDL – un mini-processeur

- 3 -

5.1 OUTILS POUR L’AIDE A LA COMPILATION ............................................................................. 17

5.1.1 Script pour le paramétrage des constantes du système ............................................... 17

5.1.2 Fichier Makefile ........................................................................................................... 19

5.2 ENTITES UTILISEES .............................................................................................................. 19

5.2.1 Upp ............................................................................................................................... 19

5.2.2 Upp_alu........................................................................................................................ 19

5.2.3 Upp_decoder ................................................................................................................ 19

5.2.4 Upp_regdriver.............................................................................................................. 20

5.3 SOURCES VHDL DES COMPOSANTS MODELISES .................................................................. 20

5.3.1 Upp.vhdl ....................................................................................................................... 20

5.3.2 Upp_alu.vhdl ................................................................................................................ 22

5.3.3 Upp_decoder.vhdl ........................................................................................................ 23

5.3.4 Upp_regdriver.vhdl ...................................................................................................... 25

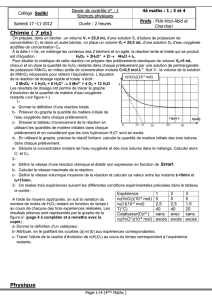

6 SIMULATIONS ...................................................................................................................... 29

6.1 SIMULATION DU CIRCUIT DE DECODAGE (UPP_DECODER) .................................................... 29

6.2 SIMULATION DU CIRCUIT D’OPERATIONS LOGIQUES ET ARITHMETIQUES (UPP_ALU)............ 29

6.3 SIMULATION DU PILOTE DE REGISTRES (UPP_REGDRIVER) ................................................... 30

6.4 SIMULATION DU COMPOSANT PRINCIPAL UPP ....................................................................... 31

7 SYNTHESE ............................................................................................................................. 32

7.1 UPP_ALU ............................................................................................................................. 33

7.2 UPP_DECODER ..................................................................................................................... 34

7.3 UPP_REGDRIVER .................................................................................................................. 35

7.4 UPP ...................................................................................................................................... 36

7.4.1 Upp, avec sa hiérarchie de composants conservée ..................................................... 36

7.4.2 Upp, hiérarchie dissoute .............................................................................................. 36

8 POUR ALLER PLUS LOIN… .............................................................................................. 38

8.1 PROGRAM COUNTER ............................................................................................................ 38

8.2 MEMOIRE CACHE ................................................................................................................. 38

8.3 PIPELINE .............................................................................................................................. 38

Projet de VHDL – un mini-processeur

- 4 -

CONTEXTE

Le VHDL (Very High speed integrated circuits Description Language) est un langage de

description matériel permettant de décrire la structure d’un design électronique, en la décomposant

en sous-blocs et en spécifiant comment ces sous-blocs sont reliés. D’autre part, il permet de décrire

le corps d’un bloc par l’intermédiaire de fonctions usuelles utilisées dans des langages de

programmation informatique.

Décrire un composant en VHDL permet de réduire le cycle de conception, en offrant un design

facilement simulable et plus facile à valider. D’autre part, les composants créés sont facilement

réutilisables et modifiables.

Dans le cadre de l’unité VHDL de I4, les étudiants doivent réaliser un projet en VHDL. Ce rapport

décrit la façon dont le projet a été mené.

Projet de VHDL – un mini-processeur

- 5 -

1 OBJECTIFS

Lorsque l’on commence un projet, il faut avoir des objectifs clairs. Nous nous sommes fixés ici

l’objectif de montrer aussi clairement que possible comment le VHDL a changé la donne en

matière de conception électronique. En particulier, il nous est paru important d’insister sur les

points suivants :

1.1 Un code réutilisable et commenté

Le code VHDL que nous écrirons sera paramétrable autant que possible. Nous maintiendrons un

fichier de constantes permettant de changer toutes les constantes du composant : taille des

registres, nombre de registres, nombre d’instructions, etc.

D’autre part, le code sera lisible et commenté, de manière à en faciliter la compréhension pour une

personne étrangère au projet.

1.2 Un code modulaire pour faciliter le travail en équipe

En VHDL, il est très facile de décomposer un composant en sous-composants. Chacun de ces sous-

composants devient un composant à part entière et doit répondre à un sous-cahier des charges. Si

chacun des sous-composants est fidèle à son sous-cahier des charges, alors les membres du groupe

de projet peuvent travailler indépendamment les uns des autres et rassembler leurs descriptions une

fois leur mission accomplie.

1.3 L’avantage de l’outil informatique

Les fichiers VHDL sont des fichiers texte à part entière. On peut donc profiter de l’avantage offert

par l’environnement de développement pour programmer des scripts informatiques qui traitent les

fichiers sources au préalable. Dans notre exemple, nous utiliserons par exemple un script Perl qui

permet de remplacer dans le code VHDL des constantes spécifiées dans un fichier principal de

constantes et de faire certains calculs comme des calculs de logarithmes (utilisés notamment pour

déterminer le nombre de fils nécessaires pour coder un nombre compris dans un intervalle de

valeurs). Nous aurons aussi un fichier makefile qui contiendra toutes les informations sur la

compilation du code et les dépendances entre fichiers.

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

1

/

39

100%