Chapitre I

1

Introduction générale

I

In

nt

tr

ro

od

du

uc

ct

ti

io

on

n

a

au

ux

x

o

or

rd

di

in

na

at

te

eu

ur

rs

s

Un ordinateur est un ensemble d’équipements chargés de traiter des données:

Ces données sont transmises par le biais d’unités d’entrée à l’unité de traitement

L’unité de traitement effectue le traitement demandé

Le résultat du traitement est transmis aux unités de sortie qui permettent alors d’exploiter

ces résultats.

Un ordinateur se présente généralement sous forme d’un boitier contenant l’unité centrale de

traitement et quelques périphériques, d’un clavier, d’une souris, et d’un écran.

L’unité centrale de l’ordinateur, ou le processeur, ou encore le microprocesseur (si

c’est un circuit intégré), est le circuit qui effectue toutes les opérations de traitement et est

donc le cerveau de l’ordinateur.

Il travaille en étroite collaboration avec la mémoire centrale (la communication entre

eux est rapide, ce qui fournit plus de puissance à la machine), avec laquelle il forme

l’unité centrale de traitement.

Unités

d’entrée

Unité de

traitement

Unités de

sortie

Introduction générale

Introduction aux ordinateurs

2

Les autres éléments de l’ordinateur clavier, souris, écran, imprimante, modem, mémoire

auxilliaire (lecteur de disquettes, disque dur, CD ROM , flash disk…), table traçante, …

sont appelés périphériques, ou unités d’entrée sortie (E/S).

La partie de l’ordinateur qui nous intéresse particulièrement est le processeur,

puisque le but de la première partie

de ce cours est la conception d’un processeur de base.

La technologie de base utilisée pour la réalisation de processeurs numériques, est

l’électronique digitale.

Tout processeur est constitué de circuits digitaux combinatoires (portes logiques,

multiplexeurs, décodeurs, additionneurs,…), et séquentiels (bascules, registres, compteurs,

mémoires, …), qui traitent, transfèrent, et mémorisent des informations, selon des règles

définies en fonction de l’organisation et de la structure de ces différents éléments. Le cours

est donc organisé de manière à rappeler des notions d’electronique digitale vues en troisième

année, et nécessaires à la conception du processeur de base, et à définir une méthode de

conception modulaire d’un processeur, actuelle, et valable pour concevoir du plus simple au

plus sophistiqué et complexe des processeurs.

Dans le premier chapitre nous rapellerons les principaux circuits combinatoires et

séquentiels succeptibles d’être utilisés dans un processeur.

Dans le chapitre 2 nous introduirons le langage de transfert inter registre (LTR), qui est un

langage de programmation de circuit (la partie hard, et non la partie soft), et qui permet de

décrire toute opération logique se déroulant dans un processeur à chaque impulsion

d’horloge.

Le chapitre 3 décrira différentes organisations de processeurs généraux classiques.

Les informations de ces trois premiers chapitres seront utilisées dans le chapitre 4 pour

effectuer les choix et hypotèses, et concevoir un processeur de base possédant un

configuration minimale, mais complète et fonctionnelle.

Le chapitre 5 conçoit une version micro programmée (unité de contrôle programmée et non

câblée) du processeur de base.

Chapitre 1

Rappels

3

Chapitre I

R

Ra

ap

pp

pe

el

ls

s

I. Introduction :

La conception du processeur de base nécessite le rappel de notions d’Electronique digitale

vues en troisième année.

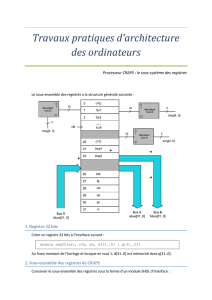

Sachant qu’un processeur est un ensemble de registres contenant des données sur lesquelles

des opérations logiques sont exécutées, selon les ordres reçus par des programmes, et transmis

à un circuit de contrôle qui activent ces opérations, on déduit qu‘un processeur, ou unité

centrale, est constitué d’une unité de contrôle et d’une unité de traitement.

Durant ce cours nous comprendrons comment tout cela fonctionne impulsion d’horloge par

impulsion d’horloge. Dans ce premier chapitre , nous commencerons par décrire les circuits

combinatoires et séquentiels de base utilisés dans un processeur.

Il est important de noter que leur étude concernera surtout leurs aspects fonctionnels, leurs

rôles, et leurs utilisations ; on supposera généralement que le circuit intégré correspondant

existe sans chercher à le construire (comme c’était le cas en troisième année).

II. Les circuits combinatoires de base :

Un processeur exécute des opérations logiques et des opérations arithmétiques sur les

données qui lui sont fournies.

La préparation et le transport des données pour le traitement : est le premier

problème à résoudre dans la conception d’un processeur. Le routage des informations, leur

transfert vers une source sélectionnée parmi plusieurs possibles, vers une destination

Unité centrale

Unité de

traitement

Unité de

contrôle

Chapitre 1

Rappels

4

sélectionnée elle aussi parmi plusieurs possibles, nécessite l’utilisation de circuits logiques

spécifiques tels que les multiplexeurs et les décodeurs..

En ce qui concerne les opérations logiques :L’algèbre de Boole spécifie que toutes les

opérations logiques peuvent être exécutées comme une combinaison de ‘AND’ et ‘NOT’,

ou ‘OR’ et ‘NOT’ . Ce sont donc des portes logiques de base qui sont utilisées.

En ce qui concerne les opérations arithmétiques : elles ont nombreuses, et les plus

connues sont l’addition, la soustraction, la multiplication, la division, l’exponentiation …

Toutes les autres pouvant être représentées comme une somme de produits et de quotients

grâce aux développements limités. La soustraction, la multiplication, et la division,

peuvent être exécutées autour de l’opération d’addition :

La soustraction peut en effet être remplacée par la somme du complément à 2, et la

multiplication et la division par une succession d’additions et de décalages.

Dans un circuit d’exécution d’opérations arithmétiques, l’additionneur apparaît comme

étant un circuit de base.

Les opérations arithmétiques et logiques sont généralement exécutées dans un circuit, qui

est le cœur de l’unité de traitement dans un processeur, appelé l’unité arithmétique et

logique ou UAL.

1 L’additionneur :

- le demi-additionneur :

C’est un circuit réalisant une opération arithmétique entre deux bits.

Les deux entrées du circuit représentent les bits x, et y à additionner, et les sorties, le bit

somme S et le bit retenue C.

s = x y

c = xy

b- circuit logique

- l’additionneur complet :

L’additionneur complet réalise l’addition de trois bits, deux bits significatifs, x et y, et la

retenue z d’une addition précédente. Les sorties s et c sont leur somme et leur retenue

respectivement.

x

y

s

c

0

0

0

0

0

1

1

0

1

0

1

0

1

1

0

1

a- Table de vérité

s

c

x

y

Chapitre 1

Rappels

5

s = x y z

c = xy + z(x y)

b- circuit logique

2 Le soustracteur complet :

Ce circuit combinatoire réalise la soustraction de deux bits x, et y en considérant la retenue de

la soustraction de deux bits de la position inférieure. L’opération de soustraction, est

cependant souvent remplacée par l’addition du complément à deux.

Les résultats du soustracteur diffèrent de ceux de l’additionneur par la valeur de la retenue (la

somme étant égale à la différence).

s = x y z

c = xy + z(x y)

b- circuit logique

3 Les décodeurs :

D’une manière générale, un décodeur est le circuit d’une fonction digitale qui traduit

l’information binaire d’un code en entrée vers un autre code en sortie.

Notre étude concernera principalement le décodeur nx2n , dont une seule des 2n sorties est

activée à la fois, pour chacune des combinaisons des n entrées. Le décodeur 2x4 ci dessous ,

montre le principe de fonctionnement du décodeur :

x

y

z

s

c

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

a- Table de vérité

x

y

z

s

c

0

0

0

0

0

0

0

1

1

1

0

1

0

1

1

0

1

1

0

1

1

0

0

1

0

1

0

1

0

0

1

1

0

0

0

1

1

1

1

1

a- Table de vérité

x

y

z

s

c

s

c

x

y

z

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

1

/

37

100%