architecture-type

ARCHITECTURE TYPE

I) Architecture élémentaire

II) La mémoire

A) Mémoire centrale (MC)

Généralités

Structure générale d’un boîtier

Classification des boîtiers

Réalisation de la MC

B) Mémoires auxiliaires

C) Gestion de la mémoire

D) Hiérarchie des mémoires

III) L’unité centrale (UC)

IV) Les bus

V) Une architecture réelle : le 8086

A) Le boîtier processeur et ses 40 broches

B) Architecture interne

C) Adresses physiques et accès mémoire

D) Segmentation mémoire

E) Pile

I) Architecture élémentaire :

- machine de Von Neumann constituée de :

- Unité centrale

- Mémoire centrale

- Interfaces d’entrée/sortie

Unité Centrale (UC)

Exécute les instructions du programme (déroulement) selon l’ordre logique voulu par le

programmeur (Unité de commande);

Assure le traitement des données (Unité de calcul).

Mémoire centrale (MC)

Mémorisation des données et du programme en cours d’exécution;

Programme = ensemble d’instructions écrites par le programmeur dans un ordre logique.

Interfaces d’entrée/sortie

Servent à communiquer avec l’extérieur :

- entrée du programme et des données

- restitution du résultat

Actuellement :

Unité d’échanges : gère les transferts d’information entre UC et périphériques

Périphériques de communication nombreux et variés :

- de sortie : écran, imprimante, table traçante, périph vocaux…

- d’entrée : clavier, souris, lecteur de codes barres, de cartes magn., crayon

optique, écran tactile…

Périphériques de stockage d’informations : mémoire externe ou auxiliaire :

- disques magnétiques ou optiques

- disquettes

- bandes magnétiques…

II) La mémoire :

A) Mémoire centrale (MC) :

Généralités

Données mémorisées sous forme de séquences binaires obtenues par codage :

Entier non signé : binaire pur

Entier signé : convention C2

Réel : convention IEEE, par ex

Chaîne de caractères : ASCII, par ex

Compilation ou assemblage => Chaque instruction est encodée dans le langage machine et

aboutit à une séquence binaire de longueur variable;

Les séquences binaires obtenues pour le programme sont rangées consécutivement en MC;

Données + Programme séquences binaires => MC = ensemble d’éléments mémoire;

n éléments mémoire constituent un mot de n bits;

mot = plus petite unité de mémoire adressable, de taille fixe sur une machine donnée;

chaque mot a une adresse distincte;

adressage = numérotation binaire séquentielle;

adresse de taille n bits => 2n adresses distinctes;

capacité maximum adressable :

adresse n bits

mot de m bits

Capacité exprimée souvent en octets

1 octet ou byte = 8 bits

Unités utilisées :

- Kilo : 1 K = 210

- Méga : 1 M = 220

- Giga : 1 G = 230

- Téra : 1 T = 240

- Péta : 1 P = 250

- Exa : 1 E = 260

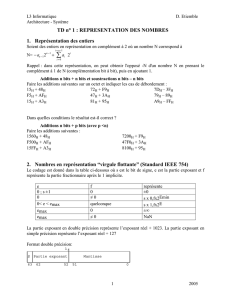

exemple 1 : mot = 1 octet = 8 bits

taille adresse = 16 bits

capacité = 216 octets = 26 Koctets = 64 Ko

= 64 x 8 K bits = 512 Kbits

exemple 2 : capacité = 2 Mbits

mot = 1 octet

2 Mbits = 2x220 bits = 218x23 bits = 218 octets

= 218 mots => adresse sur 18 bits

adressage direct <=> accès à un mot quelconque à partir de son adresse, sans parcourir les

précédents

2 opérations possibles sur la mémoire:

lecture d’un mot d’adresse donnée <=> sortie du contenu

écriture d’une information dans un mot d’adresse donnée <=> entrée de cette

information

Ces opérations mettent en jeu :

des adresses

des données

des commandes

Donnée : - lue en MC puis amenée dans l’Unité de calcul pour opération

- écrite en MC ( résultat d’un calcul)

Instruction : seulement lue en MC puis amenée dans l’UC pour y être exécutée.

Le mot mémoire d’adresse x

a pour contenu y

(x-1)

x y

=> capacité = 2n mots

= 2n x m bits

adresses contenus

(x+1)

0

Remarque : une information (donnée ou instruction) peut occuper plusieurs mots contigus

en mémoire => plusieurs lectures ou écritures nécessaires

volatilité : quand le contenu peut être perdu

temps d’accès indépendant de l’adresse

= intervalle séparant le lancement d’une opération et son accomplissement = moyenne entre

temps de lecture et temps d’écriture

Cycle mémoire = intervalle de temps entre 2 opérations successives

Cycle mémoire > temps d’accès

La MC est constituée de boîtiers mémoire

Structure générale d’un boîtier:

Matrice de points mémoire

Point mémoire = élément mémoire 1 bit

Décodeur d’adresses

= circuit de sélection du mot recherché

2 modes de sélection :

Sélection linéaire

- matrice de 2n lignes et (m + 1) colonnes

- décodeur : reçoit l’adresse n bits

active une de ses 2n sorties

- ligne activée = mot sélectionné : (m + 1) bits

- capacité = 2n mots = 2n x (m + 1) bits

Sélection à 2 dimensions

- (m + 1) plans

- un seul bit sélectionné par plan => mot = (m + 1) bits

- adresse n bits coupée en

* adresse ligne (j bits)

* adresse colonne (n - j bits)

- chaque plan possède 2 décodeurs

* décodeur ligne (active une ligne)

* décodeur colonne (active une colonne)

- point mémoire sélectionné : à l’intersection de la ligne et de la colonne

- capacité = 2j x 2n-j = 2n mots

= 2n x (m + 1) bits

Tampon d’E/S

- registre servant à stocker une donnée lue ou une donnée à écrire

- dispose de sorties 3 états

Logique de contrôle

- prend en compte les commandes émanant de l’unité de commande :

R(ead) : ordre de lecture

W(rite) : ordre d’écriture, appliqué sur la broche de lecture notée R/W

R/W = 1 => lecture commandée

R/W = 0 => écriture commandée

CS (Chip Select) ou CE (Chip Enable) : sélection du boîtier

linéaire

à 2 dimensions

Sur les boîtiers de grande capacité, remplacé par :

CAS : validation colonnes

et RAS : validation lignes

adresse entrée en 2 parties

Par multiplexage, les 2 parties d’adresse sont présentées sur les mêmes broches d’adresse =>

moins de broches.

1er temps : adresse ligne entrée et stockée dans le tampon ligne;

2ème temps : adresse colonne entrée et stockée dans le tampon colonne.

Classification des boîtiers mémoire

Mémoires mortes

une fois enregistré, contenu non volatile

ROM (Read Only Memory) :

contenu programmé par le constructeur

Seule opération possible : lecture

Utilisées pour les programmes résidents

PROM (Programmable ROM)

contenu programmable par l’utilisateur

REPROM (Reprogrammable ROM)

effacement et reprogrammation possibles mais lents.

Mémoires vives

lecture et écriture possibles.

SRAM (Static Random Access memory) point mémoire RAM ; utilisée dans les

mémoires caches;

DRAM (Dynamic RAM) régénération périodique de leur contenu ; de plus grande

capacité que les précédentes;

SDRAM (Synchronous DRAM) synchronisée avec le processeur (=> pas d’attente).

Quelques exemples de boîtiers :

- pas de broche R/W => mémoire morte

- broche de programmation => REPROM

- broche R/W => RAM

- nombre de broches d’adresse = taille de l’adresse sauf si multiplexage d’adresse

- pour une mémoire morte : nombre de broches de donnée = taille de la donnée lue

- pour une mémoire vive :

Nombre de broches de donnée en entrée

(donnée à écrire)

=

Nombre de broches de donnée en sortie

(donnée lue)

= taille de la donnée

- broches CAS et RAS <=> multiplexage de l’adresse => taille adresse = 2 x nombre de

broches d’adresse

Réalisation de la mémoire centrale

Puces ou boîtiers répartis en cartes; MC = ensemble de cartes.

Composition du mot mémoire :

un bit par carte

mot = ensemble des bits de même adresse sur chaque carte

adresse du mot = n° de la puce + adresse dans cette puce

adresse ligne

adresse colonne

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

1

/

13

100%