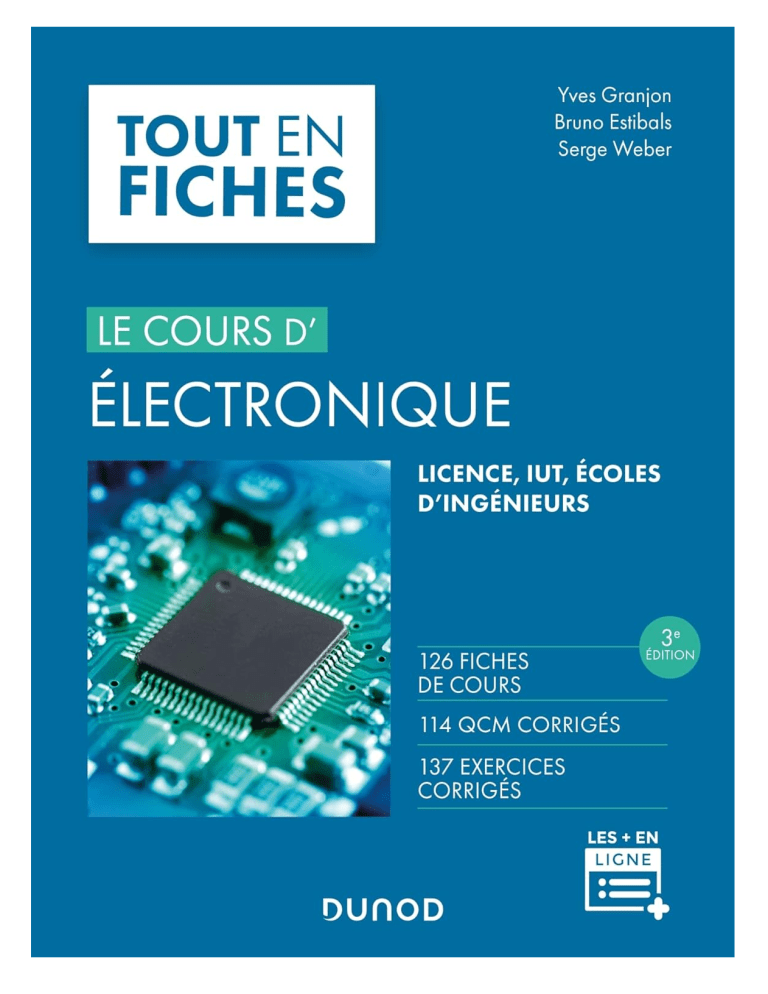

Yves Granjon est professeur à l’université de Lorraine et

directeur de l’école européenne en génie des matériaux

de Nancy.

3e

ÉDITION

Bruno Estibals est professeur à l’université Paul Sabatier

(Toulouse III) IUT-A, du département GEII.

Serge Weber est professeur à l’université de Lorraine, chef

du département électronique et électrotechnique de la

faculté des Sciences et technologie, responsable du master

Électronique, Énergie électrique, Automatique.

9782100847914-Livre.indb 3

27/11/22 16:01

Illustration de couverture : © Zyn Chakrapong – Shutterstock

© Dunod, 2015, 2019, 2023

11 rue Paul Bert, 92240 Malakoff

www.dunod.com

EAN 9782100853755

9782100847914-Livre.indb 4

27/11/22 16:01

Table des matières

Avant-propos IX

Comment utiliser cet ouvrage ?

Remerciements

Chapitre 1

Principes généraux de l’électrocinétique

1

Fiche 1

Généralités et conventions

2

Fiche 2

Les différents types de générateurs

4

Fiche 3

Les dipôles passifs linéaires usuels

6

Fiche 4

Les régimes électriques dans les circuits

8

Fiche 5

Les lois de Kirchhoff en régime continu

10

Fiche 6

Le théorème de Millman

12

Fiche 7

Les ponts diviseurs

14

Fiche 8

Le principe de superposition

16

Fiche 9

Les théorèmes de Thévenin et Norton

18

Fiche 10

Les circuits linéaires en régime sinusoïdal

20

Fiche 11

Le modèle complexe en régime sinusoïdal

22

Fiche 12

Le régime sinusoïdal – Méthode

24

Fiche 13

La puissance électrique

26

Fiche 14

La puissance en régime sinusoïdal

28

Fiche 15

La modélisation des quadripôles 1

30

Fiche 16

La modélisation des quadripôles 2

32

Fiche 17

Les schémas équivalents des quadripôles

34

Fiche 18

Le transformateur monophasé parfait

36

Fiche 19

Le transformateur monophasé réel

38

Focus

Les grands noms de l’électricité

40

QCM

41

Exercices

43

Chapitre 2

© Dunod. Toute reproduction non autorisée est un délit.

X

XIII

Signaux et systèmes

47

Fiche 20

La notion de spectre

48

Fiche 21

Le spectre des signaux périodiques

50

Fiche 22

Le spectre des signaux non périodiques

52

Fiche 23

La transformation de Laplace 1

54

Fiche 24

La transformation de Laplace 2

56

Fiche 25

La fonction de transfert d’un système

58

Fiche 26

Les méthodes de résolution des problèmes

60

Focus

Signaux analogiques et signaux numériques

62

QCM

63

Exercices

65

Chapitre 3

Les diodes

69

Fiche 27

La conduction électrique intrinsèque

70

Fiche 28

La diode à jonction

72

Fiche 29

Le principe de fonctionnement de la diode

74

Fiche 30

Les caractéristiques électriques de la diode

76

Fiche 31

La polarisation de la diode

78

Fiche 32

La puissance dissipée dans une diode

80

Fiche 33

Les applications des diodes

82

Fiche 34

Le redressement double alternance

84

V

9782100847914-Livre.indb 5

27/11/22 16:01

Fiche 35

Les régulateurs de tension

86

Focus

Les ancêtres des semi-conducteurs

88

QCM

89

Exercices91

Chapitre 4

Les transistors bipolaires

93

Fiche 36

Le transistor bipolaire

94

Fiche 37

La polarisation d’un transistor

96

Fiche 38

L’approche physique de la polarisation

98

Fiche 39

Le fonctionnement en commutation

100

Fiche 40

Les montages à plusieurs transistors

102

Focus

Toute une gamme de transistors

104

QCM

105

Exercices107

Chapitre 5

Les transistors bipolaires en régime dynamique

109

Fiche 41

Les paramètres hybrides du transistor NPN

110

Fiche 42

Le schéma équivalent du transistor

112

Fiche 43

Les amplificateurs

114

Fiche 44

L’amplificateur à émetteur commun

116

Fiche 45

L’amplificateur à collecteur commun

118

Fiche 46

L’amplificateur à base commune

120

Fiche 47

Le montage push-pull

122

Fiche 48

Le montage push-pull à correction de distorsion

124

Fiche 49

L’amplificateur différentiel simple

126

Fiche 50

La réjection du mode commun

128

Fiche 51

Le montage Darlington en régime variable

130

Focus

Les différentes classes d'amplificateurs

132

QCM

133

Exercices135

Chapitre 6

Les amplificateurs opérationnels en régime linéaire

139

Fiche 52

Les caractéristiques de l’amplificateur opérationnel

Fiche 53

Le fonctionnement linéaire de l’amplificateur opérationnel

140

142

Fiche 54

Les additionneurs et les soustracteurs

144

Fiche 55

Les montages évolués

146

Fiche 56

De la théorie à la pratique

148

Fiche 57

Les montages dérivateurs et intégrateurs

150

Fiche 58

L’oscillateur à pont de Wien

152

Focus

Quand l’électronique résout les problèmes de physique

154

QCM

155

Exercices157

Chapitre 7

Les filtres analogiques linéaires

161

Fiche 59

Les diagrammes de Bode

162

Fiche 60

Les diagrammes de Bode asymptotiques

164

Fiche 61

Les différents types de filtres

166

Fiche 62

Le filtre passif passe-bas du premier ordre

168

Fiche 63

Le filtre actif passe-bande

170

Focus

Musique !

172

QCM

173

Exercices175

VI

9782100847914-Livre.indb 6

27/11/22 16:01

Chapitre 8

Les amplificateurs opérationnels en régime non linéaire 179

Fiche 64

Le comparateur

Fiche 65

Le basculement d’un comparateur

180

182

Fiche 66

Le trigger de Schmitt inverseur

184

Fiche 67

Le trigger de Schmitt non inverseur

186

Fiche 68

Les montages astables et monostables

188

Focus

Le circuit intégré 555

190

QCM

191

Exercices193

Chapitre 9

Les transistors à effet de champ

197

Fiche 69

Les transistors à effet de champ à jonction

198

Fiche 70

La polarisation des transistors JFET

200

Fiche 71

Le schéma équivalent en régime linéaire

202

Fiche 72

Les amplificateurs à JFET

204

Fiche 73

Les transistors JFET en commutation

206

Focus

Le bruit de fond

208

QCM

209

Exercices211

Chapitre 10 Les circuits logiques combinatoires

215

Fiche 74

Les fonctions logiques

216

Fiche 75

Les nombres binaires entiers

218

Fiche 76

L’algèbre de Boole

220

Fiche 77

Les circuits logiques combinatoires

222

Fiche 78

Méthode de conception d’un circuit combinatoire

224

Fiche 79

Simplification des fonctions logiques

226

Fiche 80

Multiplexeur, démultiplexeur

228

Fiche 81

Encodeurs et décodeurs

230

Fiche 82

Le comparateur

232

Fiche 83

L’additionneur234

Fiche 84

Le soustracteur

236

Fiche 85

Les caractéristiques technologiques des circuits combinatoires

238

Focus

La logique à relais : toujours vivante

240

QCM

241

© Dunod. Toute reproduction non autorisée est un délit.

Exercices243

Chapitre 11 Les circuits logiques séquentiels

247

Fiche 86

La logique séquentielle

248

Fiche 87

La fonction séquentielle synchrone

250

Fiche 88

Les registres

252

Fiche 89

Les compteurs

254

Fiche 90

Les machines à nombre fini d’états

256

Fiche 91

L’analyse de machines d’état

258

Fiche 92

La synthèse des machines d’état

260

Fiche 93

Le graphe d’état pour les systèmes non conditionnés

262

Fiche 94

Le graphe d’état pour les systèmes à évolution conditionnelle

264

Fiche 95

Les caractéristiques temporelles des systèmes séquentiels

266

Focus

De la logique séquentielle et combinatoire au microprocesseur

268

QCM

269

Exercices271

VII

9782100847914-Livre.indb 7

27/11/22 16:01

Chapitre 12 Les technologies des circuits numériques

275

Fiche 96

Circuits TTL et CMOS

276

Fiche 97

La classification des circuits numériques

278

Fiche 98

Les circuits PLD

280

Fiche 99

Les circuits FPGA

282

Fiche 100 Mémoires, notions générales

284

Fiche 101 Mémoires RAM et PROM

286

Fiche 102 Les circuits combinatoires à base de RAM

288

Fiche 103 Les machines d’états à base de mémoire et registre

290

Focus

Évolution des mémoires DRAM

292

QCM

293

Exercices295

Chapitre 13 Éléments d’instrumentation et de mesure

299

Fiche 104 La mesure du courant

300

Fiche 105 La mesure d’une tension

302

Fiche 106 L’oscilloscope304

Fiche 107 Les sondes de courant et différentielle

306

Fiche 108 La chaîne d’instrumentation

308

Fiche 109 Les capteurs : principes généraux

310

Fiche 110 Les capteurs actifs

312

Fiche 111 Les capteurs passifs

314

Fiche 112 Les convertisseurs analogique-numérique

316

Fiche 113 Les convertisseurs numérique-analogique

318

Focus

Capteurs et automobile

320

QCM

321

Exercices323

Chapitre 14 Éléments d’électronique de puissance

327

Fiche 114 Les composants en régime de commutation

328

Fiche 115 Introduction à l’électronique de puissance

330

Fiche 116 Les hacheurs série et parallèle

332

Fiche 117 Le hacheur série en conduction continue

334

Fiche 118 Le hacheur série en conduction discontinue

336

Fiche 119 Le hacheur parallèle en conduction continue

338

Fiche 120 Le hacheur parallèle en conduction discontinue

340

Fiche 121 Les hacheurs à accumulation

342

Fiche 122 Les hacheurs à accumulation inductive en conduction continue

344

Fiche 123 Les onduleurs et la structure de pont en H

346

Fiche 124 Régime triphasé symétrique : généralités

348

Fiche 125 Régime triphasé symétrique : connexion à une charge

350

Fiche 126 Puissance en régime triphasé

352

Focus

Vers le véhicule électrique

354

QCM

355

Exercices357

Corrigés des exercices

361

Annexes455

Index461

VIII

9782100847914-Livre.indb 8

27/11/22 16:01

© Dunod. Toute reproduction non autorisée est un délit.

Avant-propos

L’électronique est la discipline qui s’intéresse aux dispositifs électriques construits autour

de la technologie des semi-conducteurs. La plupart du temps, les courants et les tensions

mis en œuvre restent de faible amplitude, excepté en électronique de puissance.

Le traitement du signal, les automatismes, l’informatique et d’une manière plus générale, une grande partie des appareils que nous utilisons quotidiennement possèdent des

systèmes électroniques. Que ce soit pour la commande des processus, le traitement de

l’information, le contrôle ou la mesure des phénomènes, l’électronique apporte des solutions simples, fiables et souples à un grand nombre de problèmes techniques.

Cet ouvrage rassemble toutes les notions fondamentales de l’électronique : de la diode

à jonction jusqu’aux systèmes logiques, en passant par les montages à transistors et à

amplificateurs opérationnels. Il aborde également les bases de l’électronique de puissance

qui, traditionnellement, sont plutôt étudiées en électrotechnique mais dont nous avons

estimé qu’elles avaient leur place au sein d’un ouvrage consacré à l’électronique.

Il est structuré en cent-vingt-six fiches et en quatorze chapitres développant chacun

un thème particulier. Chaque fiche aborde un composant, un montage ou un principe.

À la fin de chaque chapitre, le lecteur pourra pousser sa réflexion un peu plus loin à l’aide

des focus proposés qui mettent en exergue des thématiques particulières. Après un QCM

qui lui permettra de tester ses connaissances et de valider ses acquis, il pourra ensuite

s’entraîner avec des exercices et des problèmes entièrement corrigés. Les solutions sont

présentées dans leurs moindres détails en insistant systématiquement sur les méthodes

à assimiler et sur le savoir-faire à acquérir absolument pour être capable de résoudre

n’importe quel problème d’électronique. Chaque chapitre propose des exercices de difficultés variées. Il est conseillé de les aborder dans l’ordre, sans chercher à brûler les étapes

en négligeant tel ou tel qui paraît trop facile et sans succomber à la tentation de lire trop

rapidement la solution. Certains de ces exercices sont de grands classiques ; d’autres sont

plus originaux. Ils ont tous vocation à guider l’étudiant vers la maîtrise de l’électronique

et des fonctions qu’elle permet de réaliser, et de l’aider à acquérir suffisamment d’aisance

pour aborder avec succès des problèmes de plus en plus sophistiqués.

L’électronique n’est pas une discipline extrêmement compliquée pour qui l’aborde avec

rigueur et méthode. Elle nécessite toutefois que le lecteur soit familiarisé avec les lois

fondamentales de l’électrocinétique, que ce soit en régime continu, sinusoïdal ou transitoire. Ces notions sont rappelées dans le premier chapitre qui rassemble les principaux

résultats et théorèmes qu’il est indispensable de connaître.

Les prérequis de mathématiques de l’électronique ne sont pas nombreux : ils concernent

l’analyse des fonctions réelles, le calcul différentiel et intégral et les nombres complexes.

Le formulaire situé en annexe à la fin de l’ouvrage regroupe toutes les formules de mathématiques utiles à l’électronicien.

Cet ouvrage a été conçu avec le souci constant de rendre l’électronique accessible au

plus grand nombre. Nous souhaitons que chaque lecteur puisse y trouver les clés de sa

réussite.

IX

9782100847914-Livre.indb 9

27/11/22 16:01

Comment utiliser

1

Chapitre

raux

es géné

Princip ocinétique

ctr

de l’éle

14 chapitres

auquels sont associés des bonus

web à retrouver sur dunod.com

-

tifs

Objec

126 fiches de cours

Les notions essentielles avec des renvois

pour naviguer d’une fiche à l’autre

12 Le régime sinusoïdal – Méthode

Fiche 12

Et :

p

Ê jRCw

ˆ

j = argU = arg Á

Eeff ˜ = arg( jRCw ) - arg( jRCw + 1) = - arctan( RCw ).

2

Ë jRCw + 1

¯

fiche

D’où : u(t ) = Ueff 2 cos (wt + j ).

1. La transposition au modèle complexe

Soit : u(t ) = Eeff 2

RCw

R 2C 2w 2 + 1

(

cos wt +

)

p

- arctan( RCw ) .

2

Important

Exemple

1

jCω

C

A

e (t)

→

u(t )

R

arg(a + jb) = arctan

A

E = Eeff

a

R

arg(a + jb) = arctan

U

Ce sont ces propriétés qui sont couramment utilisées pour calculer les modules et

arguments des nombres complexes en électrocinétique.

3. Le principe général

12.1.b) et

Dans la représentation complexe, en prenant soin de considérer l’impédance complexe

de chaque dipôle, les lois et théorèmes fondamentaux de l’électricité qui gouvernent les

circuits en régime continu restent valables en régime sinusoïdal : lois de Kirchhoff, théorème de Millman, principe de superposition, théorèmes de Thévenin et de Norton. Les

règles qui régissent les associations de dipôles sont également transposables au modèle

complexe.

on y applique le principe du pont diviseur de tension :

jRCw

E =

Eeff .

U =

1

jRCw + 1

R+

jCw

R

2. Le retour au modèle temporel

On a : U = Ueff e jj =

Soit : Ueff = U =

24

jRCw

Eeff .

jRCw + 1

RCw Eeff

1 + R 2C 2w 2

.

Important

Dans le schéma électrique transposé à sa représentation complexe, toutes les lois de

l’électricité valables pour le régime continu, s’appliquent aux grandeurs et variables

complexes.

Chapitre 1

Nous savons déjà que la tension u(t) est sinusoïdale de même pulsation que e(t) puisque

-

sage par rapport à e : u(t ) = Ueff 2 cos(wt + j ).

© Dunod. Toute reproduction non autorisée est un délit.

Fiche 15

b

pour a > 0

a

b

± p pour a < 0

a

b

Figure 12.1

Des

renvois

entre

fiches

Exercices

De même qu’il ne faut jamais oublier que le module d’un quotient est égal au quotient

des modules, il faut également se souvenir que l’argument d’un quotient est égal à la

différence entre l’argument du numérateur et celui du dénominateur.

Le lecteur devra également se souvenir des propriétés suivantes :

12.1.a, on cherche à déterminer l’expression de u(t).

De très

nombreux

schémas

QCM

expressions de grandeurs électriques, courants ou tensions, dans un montage alimenté

par une source sinusoïdale, par exemple e(t ) = Eeff 2 cos wt .

Si la méthode présentée ici est simple dans son principe, il n’en demeure pas moins

qu’elle exige une bonne maîtrise de la manipulation des nombres complexes. On trou-

Des conseils

méthodologiques

utiles dans ce domaine, entre autres. Il est recommandé de s’exercer autant que de besoin

sinusoïdal.

25

X

9782100847914-Livre.indb 10

27/11/22 16:01

cet ouvrage ?

Des exercices

en fin de chapitre

pour réviser (corrigés

en fin d’ouvrage)

Fiche

Des QCM

en fin de chapitre

pour s’auto-évaluer

formé par cette

association.

R3 = 60 Ω

QCM

Exercices

R4 = 25 Ω

R2 = 50 Ω

B

1.1

U inconnue.

1.2

E= 5V

A

I = 0,3 A

R= 8 Ω

B

1.2

U=?

U inconnue.

1.3

1.3

A

I = 0,1 A

E = 15 V

R= 30 Ω

B

R4

R2

© Dunod. Toute reproduc

tion non autorisée

39

est un délit.

A

1.5

B

© Dunod. Toute

E

R5

I

Des focus sur une page

à la fin de chaque chapitre

Millman est une

conséquence direct

e:

a. de la loi des

mailles

nœuds

c. du théorèRéponse

me de Thévenin

s

L’impédance d’une

1.1

bobin

a. et

e :b. Le courant est

imposé à la fois

a. est propo

par le générateur

qui àlui est conne

rtionnelle

mais aussi et surtou

son inductance

cté.

t par le circuit

propre

b. dépend de

1.2

b. La

la pulsat

ionrépon

se a qui

du signal

conce

rne l’asso

la traver

se ciation en série

c. dépend de

condu

de deux résista

l’amplitude ctance

est égale à l’inver

nces. Rappelons

du couran

se

que la

lèle, ce sont bient qui la traverse de la résistance et dans le cas

d’une association

1.6 Laquelle ou

les inverses des

résistances qui

en parallesquelles de ces

s’additionnent.

trois équations

1.3 c. Le farad

(sont)

est l’unité deest

a. U = U e jj

nature

capacité.par

(s) :

eff

Le siemensfausse

est l’unité

de conductance

1.4 b. Voir fiche

.

6.

jRC w

b. u(t ) =

E eff

1.5

jRC

w + 1 a.

et b. L’expression

Z = Lw montre

c. U e jj =

effectivement que

Ueff costions

eff

(wt + qui

ce sont les deux

j ) sont correctes.

premières propo

si1.7 Un dipôle est 1.6 b. et c.

Ne pas mélanger

alimenté par une

source de tensiomodèles compl

n sinusoïdale. exes et représentati

associés mais

a. est celle qui

ons temporelles.

est dissipée dans il ne peut y avoir égalité La puissance active

Les deux sont

les éléments résisti

entre eux. La seule :

correspond à la

fs du dipôle

écriture correc

b. est la puissa

proposition a dans

te est celle qui

nce àmoyenne conso

laquelle la forme

un nombre compl

compl

mmée

exe d’une tensio

exe.par le dipôle

c. est la puissa

n est bien égale

moyenne fourni

1.7nce a.,

e par le générateur

b. et c. Les trois

propositions sont

1.8 Lorsque deux

exactes. Voir fiche

quadr

14.

1.8 ipôles

sont

a. Voir

associ

fiche

17. és en cascade :

a. leurs matric

es impédance s’ajou

tent

b. leurs matric

es de transfert

se multiplient

c. leurs matric

es admittances

se multiplient

Chapitre 1

R3

R1

Le théorème de

b. de la loi des

Chapitre 1

est un délit.

électrique simple

alimenté par un

générateur de tensio

a. les électro

n continue parfai

ns circulent toujou

t:

rs vers la borne

positive du génér

b. le couran

ateur

t électrique circule

vers la borne négati

ve du générateur

c. le couran

t est imposé au

circuit par le génér

ateur

Lorsque deux résista

nces sont placée

s en parallèle :

a. leurs résista

nces s’ajoutent

b. leurs condu

ctances s’ajoutent

c. leurs résista

nces se multiplient

L’unité d’inductance

propre d’une bobin

e est :

a. le farad

b. le siemens

1.4

dans R5 soit

le courant I

de

ière à ce que

er l’expression

, R , R4, de man

. Puis détermin

1.4

tances R1, R2 3

ression de VA

les quatre résis

déterminer l’exp

condition sur

que I est nul,

ant

idér

nul. En cons

recherchée.

ition

cond

la

ire

VB. En dédu

non autorisée

Dans un circuit

c. le henry

U=?

reproduction

Pour chaque quest

ion, cocher la

ou les réponse(s)

réponses sont

exacte(s) (les

au verso).

Fiche

A

QCM

R1 = 100 Ω

Exercices

ainsi

1.1

du dipôle AB

équivalente

la résistance

QCM

S

EXERCICE

37

FO CUS Le bruit de fond

Les dispositifs électroniques délivrent, captent, mesurent, transforment et traitent des signaux élec-

© Dunod. Toute reproduction non autorisée est un délit.

être sensibles par exemple aux signaux électromagnétiques ambiants, les capter et les mélanger aux

signaux utiles. Ils peuvent aussi produire eux-mêmes de tels signaux parasites comme par exemple le

bruit de fond. Il s’agit là d’un phénomène dû en particulier au mouvement erratique des électrons dans

les conducteurs qui génère des forces électromotrices aléatoires qui se superposent aux signaux traités.

Si on reprend l’exemple d’un ampli audio, nous avons tous constaté qu’en l’absence de signal et en

38

t

La détection synchrone

ce qui concerne sa composition spectrale. Ainsi, il est fréquent que le bruit soit plus important dans les

basses fréquences. Dans ces conditions, une astuce consiste à décaler le spectre des signaux utiles vers

spectrale initiale. Cette technique s’appelle la détection synchrone.

S’il est impossible de décrire temporellement le bruit a priori, il est néanmoins possible, à partir de ses

Les réponses

commentées au verso

Le rapport signal sur bruit

le rapport signal sur bruit, qu’on préfère en général exprimer en décibels. Toute la problématique, en

pact sur les signaux utiles.

On peut aussi utiliser des composants électroniques haut de gamme qui produisent peu de bruit ou

déployer des dispositifs, parfois assez complexes, pour réduire le bruit. Par exemple, le système Dolby,

200

XI

9782100847914-Livre.indb 11

27/11/22 16:01

9782100847914-Livre.indb 12

27/11/22 16:01

Remerciements

© Dunod. Toute reproduction non autorisée est un délit.

Les auteurs tiennent à remercier très sincèrement les personnes suivantes pour leurs

relectures et conseils tout au long de la rédaction de cet ouvrage :

• Sylvie Roux, professeur agrégé de physique appliquée, IUT A Paul Sabatier, département GEII, Toulouse

• Frédéric Morancho, professeur des universités, université Paul Sabatier, Toulouse

• Farid Meibody-Tabar, professeur des universités, École nationale supérieure d’électricité et de mécanique de Nancy

• Guy Schneider, professeur agrégé de physique appliquée, CPP - La Prépa des INP,

Nancy

• Yves Berviller, maître de conférences, université de Lorraine, faculté des sciences et

technologies

• Slavisa Jovanovic, maître de conférences, université de Lorraine, faculté des sciences

et technologies

XIII

9782100847914-Livre.indb 13

27/11/22 16:01

9782100847914-Livre.indb 14

27/11/22 16:01

Chapitre 1

Principes généraux

de l’électrocinétique

Objectifs

Avec les spécificités qui lui sont propres, l’électronique reste un domaine qui

s’intègre dans la discipline de l’électricité générale. À cet égard, les lois, les principes fondamentaux, les théorèmes et les méthodes développées pour résoudre

les problèmes sont les mêmes. Ce chapitre rassemble les outils génériques de

l’électrocinétique qui sont utiles à l’étude des circuits électroniques. Le lecteur

y retrouvera tous les théorèmes fondamentaux ainsi que les méthodes qui sont

propres à chaque type de régime de fonctionnement des circuits.

9782100847914-Livre.indb 1

27/11/22 16:01

fiche

1

Généralités et conventions

1. Définitions et principes fondamentaux

D’une manière générale, tout circuit électrique peut se représenter sous la forme d’un

générateur d’énergie alimentant un récepteur chargé de transformer l’énergie électrique

reçue en une autre forme exploitable, les deux dispositifs étant reliés par des conducteurs.

Tout circuit électrique est le siège d’un transfert de charges entre ces deux éléments

(figure 1.1). Il est couramment admis de représenter ce transfert par un flux d’électrons

que l’on modélise par un courant électrique traversant les conducteurs.

flux d’électrons

courant i

+

générateur

récepteur

Figure 1.1

Ce courant électrique (exprimé en ampères) représente la quantité de charges q (en

coulombs) traversant une section donnée du conducteur par unité de temps. Les électrons possédant une charge négative, la logique veut que le courant i soit représenté en

sens contraire du flux d’électrons. Dans un circuit composé d’une seule boucle, le même

courant circule à chaque instant dans tout le circuit.

Générateurs et récepteurs simples possèdent en général deux bornes. Ce sont des

dipôles électriques. Les dipôles générateurs sont dits actifs, ceux qui ne font que

consommer de l’énergie sont des dipôles passifs.

2. Le générateur de tension parfait

Le dipôle actif le plus simple est le générateur de tension continue parfait qui délivre

une tension E constante (en volts) et l’impose au dipôle récepteur qui présente donc à

ses bornes la même tension E. Le courant qui apparaît alors dans le circuit dépend de E

et de la nature du récepteur. Cette tension E est la différence de potentiel VA - VB. La

flèche symbolisant cette différence de potentiel est dirigée vers le potentiel le plus élevé.

Comme les électrons sont attirés par le point A, correspondant au potentiel le plus

élevé, le courant sera naturellement orienté, au sortir du générateur, par une flèche

dirigée dans l’autre sens.

Pour un circuit alimenté par un générateur de tension, on considère en général que sa

borne B constitue la référence de tension pour l’ensemble du circuit et se trouve donc au

potentiel 0 V (on dit aussi à la masse). Sa borne A se trouve donc au potentiel VA = E .

2

9782100847914-Livre.indb 2

27/11/22 16:01

Fiche 1

On assimile donc toute différence de potentiel entre un point X quelconque et cette

référence, au potentiel du point X.

courant

A

+

VA − VB = E

E

QCM

E

B

générateur

de tension

parfait

récepteur

Exercices

Figure 1.2

3. Conventions

Dans un circuit simple composé d’un générateur de tension et d’un dipôle récepteur, compte

tenu du fait que la même tension règne aux bornes des deux éléments, et que le même

courant circule dans tout le circuit, on note que du côté du générateur, courant et tension

sont représentés par des flèches dirigées dans le même sens, alors que du côté du récepteur,

elles sont dirigées en sens contraires (figure 1.3). Par convention, nous dirigerons systématiquement les flèches des courants et des tensions dans le même sens pour le générateur

(convention générateur), et en sens contraires pour tout récepteur (convention récepteur).

En règle générale, les circuits simples ne comportent qu’un seul générateur. Toutefois,

certains peuvent en contenir plusieurs. Dans ce cas, si un générateur est considéré

comme appartenant à la partie réceptrice du circuit, c’est la convention récepteur que

nous utiliserons.

A

convention

générateur

E

E

B

Chapitre 1

© Dunod. Toute reproduction non autorisée est un délit.

convention

récepteur

i

i

Figure 1.3

Le respect des conventions de signes est absolument essentiel dans la résolution d’un

problème d’électricité en général et d’électronique en particulier. La plupart des erreurs

proviennent du non respect de ces règles élémentaires.

On retiendra notamment qu’en général, on n’utilise la convention générateur que pour

le générateur principal du circuit.

3

9782100847914-Livre.indb 3

27/11/22 16:01

fiche

2

Les différents types de générateurs

1. Le générateur de courant continu parfait

Fiche 1

Outre le générateur de tension parfait, un circuit peut être alimenté par un générateur de

courant parfait (figure 2.1).

Ce dernier impose un courant I au dipôle récepteur. La tension qui apparaît alors aux

bornes du dipôle récepteur dépend de I et de la nature du récepteur.

Les générateurs de courant sont en général des dispositifs complexes utilisés dans des

cas bien particuliers.

courant I

A

tension V

I

B

générateur

de courant

parfait

récepteur

Figure 2.1

Important

Les générateurs sont dits parfaits au sens où la tension délivrée par un générateur de

tension parfait ne dépend pas du reste du circuit. De même, un générateur de courant

parfait délivre un courant qui ne dépend pas du reste du circuit.

2. Le générateur de tension réel

Dans la réalité, un générateur de tension n’est jamais parfait. La tension qu’il délivre

diminue plus ou moins selon l’intensité du courant qu’on lui soutire. Ce phénomène est

dû à la superposition de diverses chutes de potentiel internes qui ne peuvent plus être

négligées lorsque le générateur est parcouru par un courant intense.

On considère alors qu’un modèle plus proche de la réalité consiste à associer une résistance en série avec un générateur de tension parfait, ou une résistance en parallèle avec

un générateur de courant parfait. Ces résistances sont appelées résistances internes des

générateurs (figure 2.2).

Si I est le courant qui circule dans le circuit, on a : VA - VB = E - rI .

4

9782100847914-Livre.indb 4

27/11/22 16:01

courant I

Fiche 2

A

r

générateur

de tension

réel

VA − VB ≠ E

E

QCM

B

récepteur

Figure 2.2

3. Le générateur de courant réel

Exercices

De la même manière, un générateur de courant réel sera modélisé par la mise en parallèle

d’un générateur de courant parfait et d’une résistance dite interne (figure 2.3).

Dans ce cas, le courant qui alimente le récepteur est plus faible que le courant délivré

par le générateur parfait et dépend de la tension qui s’installe aux bornes du récepteur.

courant ≠ I

A

I

r

B

générateur

de courant

réel

récepteur

Figure 2.3

Outre les générateurs continus qui délivrent des tensions ou des courants constants, il est

très fréquent d’utiliser des générateurs de signaux variables dans le temps et de formes

variées (signaux sinusoïdaux, par exemple, ou autres signaux périodiques, etc.). D’une

manière générale, on réserve les lettres majuscules pour nommer les grandeurs continues

(VA , E , I 0 ) et les lettres minuscules pour les grandeurs variables ( v , e1 , in).

Dans tous les cas, lorsqu’il s’agit du générateur principal du circuit, on utilisera la

convention générateur pour repérer le sens de la tension à ses bornes et celui du courant

qu’il délivre (flèches dirigées dans le même sens).

Chapitre 1

© Dunod. Toute reproduction non autorisée est un délit.

4. Les autres générateurs

5

9782100847914-Livre.indb 5

27/11/22 16:01

fiche

3

Les dipôles passifs linéaires usuels

1. Les lois de fonctionnement élémentaires

Trois dipôles passifs sont couramment utilisés dans les circuits électroniques. Ils ont la

particularité de posséder un fonctionnement qui s’exprime sous la forme d’une équation

différentielle simple, linéaire, à coefficients constants. L’équation de fonctionnement d’un

dipôle lie la tension à ses bornes et le courant qui le traverse. En supposant que, dans le

cas le plus général, ces deux grandeurs sont variables dans le temps, les lois de fonctionnement des trois dipôles passifs usuels sont présentées sur la figure 3.1.

résistance

bobine

i(t )

u(t )

R

condensateur

i(t )

u(t )

u(t ) = Ri(t)

i(t )

u(t )

u(t ) = L

di

dt

R : résistance

L : inductance propre

en ohms (Ω)

en henrys (H)

u(t)= i

1

i(t)dt

C∫

C : capacité

en farads (F)

Figure 3.1

2. Associations de dipôles

Deux dipôles quelconques sont dits associés en série si une des bornes de l’un est reliée

à une des bornes de l’autre, l’ensemble formant un nouveau dipôle. Ils sont dits associés

en parallèle si les paires de bornes sont connectées deux à deux (figure 3.2).

Dans le cas de l’association en série, les deux dipôles sont parcourus par le même

courant. La tension totale aux bornes de l’ensemble est égale à la somme des deux différences de potentiel aux bornes de chacun des deux dipôles.

Dans le cas de l’association en parallèle, la même différence de potentiel règne aux

bornes de chacun des deux dipôles.

En tenant compte de ces constats, on peut en déduire les règles d’association des différents dipôles.

6

9782100847914-Livre.indb 6

27/11/22 16:01

Fiche 3

E1

E1

E2

E2

I1

E 1= E 2

I2

QCM

E 1+ E 2

I = I1 + I 2

association

en série

association

en parallèle

Exercices

Figure 3.2

En associant des résistances, on forme un dipôle qui se comporte comme une résistance, dont la valeur est appelée résistance équivalente, que l’on note en général Req .

Lorsque l’on associe des condensateurs, on forme un condensateur équivalent de

capacité Ceq.

Lorsque deux résistances R1 et R2 sont associées en série, on a Req = R1 + R2 .

Lorsqu’elles sont associées en parallèle, on a

R1 R2

1

1

1

=

+

, soit Req =

.

R1 + R2

Req

R1 R2

Lorsque deux condensateurs C1 et C2 sont associées en série, on a

1

1

1

=

+

.

Ceq C1 C2

Lorsqu’ils sont associés en parallèle, on a Ceq = C1 + C2.

Attention

Les règles qui régissent l’association de bobines sont les mêmes que celles qui

concernent les résistances : les inductances s’additionnent lorsque les bobines sont

placées en série. Leurs inverses s’ajoutent lorsqu’elles sont placées en parallèle.

L’ensemble des résultats présentés ici se généralisent sans problème à l’association série

ou parallèle de n éléments différents.

Il est possible de simplifier les circuits électriques en calculant les valeurs équivalentes

d’une combinaison plus ou moins complexe de dipôles. On procède alors de proche en

proche en recherchant les associations les plus simples et en réduisant ainsi pas à pas le

circuit initial.

Chapitre 1

© Dunod. Toute reproduction non autorisée est un délit.

On remarquera que les règles d’associations des résistances et celles d’associations des

condensateurs se trouvent inversées.

7

9782100847914-Livre.indb 7

27/11/22 16:01

fiche

4

Les régimes électriques dans les circuits

Selon la forme de la tension (ou du courant) délivrée par le générateur qui alimente un

circuit, on dit que ce circuit fonctionne selon un certain régime.

1. Le régime continu

Lorsqu’un circuit est alimenté par un générateur qui délivre une tension constante, on

dit qu’il fonctionne en régime continu. Les régimes continus font partie des régimes

dits permanents ou établis. Dans un circuit fonctionnant en régime continu, toutes les

tensions et tous les courants dans le circuit sont en général continus.

Rappel

Les grandeurs continues sont notées avec des lettres majuscules (E pour une tension,

par exemple).

En régime continu, un élément inductif (une bobine) n’a aucun effet. Son équation de

fonctionnement montre que, parcourue par un courant constant quelconque, une bobine

présente toujours une différence de potentiel nulle à ses bornes :

u(t ) = L

di

fi u(t ) = 0 si i = C te .

dt

Un condensateur, en régime continu, n’est parcouru par aucun courant :

u(t ) =

1

i (t ) dt fi i (t ) = 0 si u(t ) = C te .

Ú

C

Remarque

Si aucun courant ne peut traverser un condensateur en régime continu, tout condensateur

qui se voit imposer une tension U présente bel et bien une charge emmagasinée Q telle que

Q = CU . Un condensateur parfait possède en outre la propriété de conserver cette charge

emmagasinée, une fois l’alimentation U coupée. Ceci, bien évidemment, à condition qu’il

soit isolé, c’est-à-dire que ses deux bornes ne soient reliées à aucun autre circuit.

2. Le régime sinusoïdal

Lorsqu’un circuit est alimenté par un générateur qui délivre une tension sinusoïdale

e(t ) = E0 cos wt , le régime sera dit sinusoïdal ou harmonique.

Les régimes sinusoïdaux font également partie des régimes dits permanents ou établis.

Dans un circuit fonctionnant en régime sinusoïdal, tensions et courants sont tous sinusoïdaux, de même pulsation w que la source de tension, mais présentant a priori des déphasages.

8

9782100847914-Livre.indb 8

27/11/22 16:01

3. Le régime transitoire

A

A

QCM

E

⇔ e (t )

E

e (t )

t

0

B

B

a

b

c

Exercices

K

Fiche 4

Les régimes transitoires correspondent en général au passage d’un régime permanent à

un autre régime permanent. Ces changements de régime sont la plupart du temps dus à

l’ouverture ou à la fermeture d’un interrupteur dans le circuit ou encore à la présence de

composants agissant comme des interrupteurs.

Figure 4.1

Dans le circuit représenté sur la figure 4.1.a, le dipôle AB est alimenté par un générateur parfait de tension constante E par l’intermédiaire d’un interrupteur K. Lorsqu’on

ferme l’interrupteur, tout se passe comme si on passait brusquement d’un régime permanent e(t ) = 0 à un autre régime permanent e(t ) = E . Le dipôle est en quelque sorte

alimenté par la tension e(t ) (figure 4.1.b).

Il suffit de considérer que l’instant t = 0 correspond à l’instant de fermeture de l’interrupteur. Comme un interrupteur n’est pas un élément linéaire, on préfère utiliser le

modèle représenté sur la figure 4.1.b, dans lequel le circuit est linéaire (schéma sans

interrupteur), mais dans lequel la forme de la tension d’alimentation n’est pas constante

mais se présente sous la forme d’un échelon (figure 4.1.c).

Important

Les problèmes à résoudre sont en général toujours les mêmes : il s’agit de déterminer

tensions et courants dans le circuit. Comme celui-ci n’est pas alimenté par une tension

constante ou sinusoïdale, tous les courants et toutes les tensions dans le circuit seront a

priori variables.

La résolution des problèmes d’électricité en régime transitoire se traduit en général par

des équations différentielles. Les plus simples, comme par exemple les équations différentielles linéaires à coefficients constants d’ordre peu élevé se résolvent directement

avec une relative facilité. Pour les autres, des outils plus performants seront nécessaires

comme la transformée de Laplace, voire des méthodes numériques.

Chapitre 1

© Dunod. Toute reproduction non autorisée est un délit.

Les régimes transitoires peuvent intervenir aussi bien à l’ouverture qu’à la fermeture

d’interrupteurs, ou encore au basculement de commutateurs. D’une manière générale,

le régime transitoire conduit toujours le système vers un régime permanent.

9

9782100847914-Livre.indb 9

27/11/22 16:01

fiche

5

Les lois de Kirchhoff en régime continu

1. Définitions

• Réseau électrique : toute association simple ou complexe de dipôles interconnectés,

alimentée par un générateur.

• Branche : partie dipolaire d’un réseau parcourue par un même courant.

• Nœud d’un réseau : tout point du réseau commun à plus de deux branches.

• Maille d’un réseau : tout chemin constituant une boucle et formé de plusieurs

branches.

Sur le circuit de la figure 5.1, l’association de R1, R2 , R3, R4 et R5 formant le dipôle

AC constitue un réseau électrique alimenté par le générateur de tension E. A, B, C et D

sont les nœuds de ce réseau. Le schéma montre trois mailles. Il en existe d’autres, par

exemple, en partant du point A, on peut définir une maille qui comprend R2 , R3 et R5,

qui passe par D, puis C et qui rejoint A en incluant R1.

I0

R2

A I2

E2

I1

R1

E

R3

B I3

R4

E1

maille 1

maille 2

C

E3

E4

I4

R5

E5

maille 3

D

Figure 5.1

2. La loi des nœuds

La somme des courants se dirigeant vers un nœud est égale à la somme des courants qui

sortent de ce nœud.

Ou encore : la somme algébrique des courants dirigés vers un nœud d’un circuit est

nulle (en comptant positivement les courants dirigés vers le nœud et en comptant négativement ceux qui en sortent).

Cette loi exprime le fait qu’il ne peut pas y avoir accumulation de charges en un point

quelconque d’un conducteur du réseau. Dans l’exemple de la figure 5.1, on pourra écrire

entre autres équations : I 0 = I1 + I 2 et I 2 = I 3 + I 4.

10

9782100847914-Livre.indb 10

27/11/22 16:01

3. La loi des mailles

Fiche 5

La somme algébrique des différences de potentiel le long d’une maille, obtenue en

parcourant la maille dans un sens donné, est nulle. Les différences de potentiel orientées

dans le même sens que le sens de parcours de la maille sont comptées positivement. Les

différences de potentiel orientées dans le sens opposé au sens de parcours de la maille

sont comptées négativement.

Ainsi, dans l’exemple de la figure 5.1 :

QCM

Maille 1 : E - E1 = 0

Maille 2 : E1 - E2 - E4 = 0

Maille 3 : E4 - E3 - E5 = 0

Note

Exercices

Les lois de Kirchhoff sont présentées ici en régime continu (lettres majuscules pour les

tensions et les courants). En réalité, elles restent valables quel que soit le régime.

4. La loi des nœuds généralisée

Dans un dispositif électrique quelconque, la somme algébrique des courants entrant (ou

n

sortant négativement) dans une surface fermée est nulle : Â I i = 0 (figure 5.2).

i =1

I1

I2

circuit

I3

Figure 5.2

D’un point de vue pratique, cela signifie que dans un circuit complexe, on peut définir

arbitrairement un contour fermé et appliquer la loi des nœuds aux bornes de ce contour.

Chapitre 1

© Dunod. Toute reproduction non autorisée est un délit.

In

Remarque

Il est assez rare d’utiliser les lois de Kirchhoff pour résoudre entièrement un problème

d’électricité. En effet, elles génèrent beaucoup d’équations et beaucoup d’inconnues et on

leur préfère des théorèmes plus puissants.

11

9782100847914-Livre.indb 11

27/11/22 16:01

fiche

6

Le théorème de Millman

Le théorème de Millman permet d’exprimer le potentiel en un nœud quelconque d’un

réseau en fonction des potentiels aux nœuds voisins. Il est une conséquence de la loi des

nœuds et peut donc être utilisé à sa place. L’avantage réside dans le fait qu’on exprime des

relations sans courant, uniquement à l’aide de tensions. En utilisant à la fois le théorème

de Millman et la loi des mailles, on dispose de deux outils qui permettent de résoudre

pratiquement n’importe quel problème d’électrocinétique.

Considérons un nœud quelconque d’un circuit (figure 6.1). Ce nœud est relié à n points

du circuit par l’intermédiaire de n branches possédant chacune une résistance Ri . Soient

Vi les tensions aux n points voisins du nœud X.

V3

V2

R2

V1

R1

R3

Ri

X

Vi

VX

Rn

Vn

Figure 6.1

Le potentiel VX s’exprime en fonction des potentiels aux nœuds voisins de la manière

suivante :

n

Vi

V

V1 V2

+

+◊◊◊+ n

Â

R

R

R2

Rn

VX = 1

= i =n1 i

1

1

1

1

+

+◊◊◊+

ÂR

R1 R2

Rn

i

i =1

On peut définir également la conductance d’un dipôle résistif par l’inverse de sa résistance. Soit :

1

Gi =

unité : siemens ( S ).

Ri

Ainsi, le théorème de Millman peut aussi s’écrire :

n

GiVi

VX = i =1n

Gi

.

i =1

12

9782100847914-Livre.indb 12

27/11/22 16:01

Fiche 6

Ce qui revient à dire que le potentiel en un nœud quelconque d’un circuit est la moyenne

des potentiels aux nœuds voisins, pondérée par les conductances des différentes branches.

Exemple

E1 = 10V

A

R2 = 5 Ω

R3 = 20 Ω

E2 = 5 V

Exercices

R1 = 10 Ω

QCM

On considère le circuit de la figure 6.2 dans lequel on cherche à calculer le potentiel au

point A. L’application du théorème de Millman en ce point est immédiate.

Attention : même si la résistance R3 est reliée à la masse et qu’elle ne correspond à aucun

terme au numérateur, elle est néanmoins présente au dénominateur.

Figure 6.2

Le théorème de Millman est un outil extrêmement intéressant, surtout si on le compare

aux lois de Kirchhoff :

• Comme il découle de la loi des nœuds mais ne met en équation que des tensions, il

permet de limiter le nombre de variables introduites dans les équations.

• Il permet de cibler le calcul d’un potentiel particulier ou d’une différence de potentiels

donnée en n’écrivant qu’une seule ligne de calcul. Ne pas oublier que bien souvent,

on cherche la valeur d’une tension particulière et que la connaissance de toutes les

grandeurs électriques, courants ou tensions, en tout point du circuit, ne sert pas à

grand chose.

• Il s’applique tout aussi bien en régime continu qu’en régime variable.

• Dans le cas de circuits plus complexes que celui qui est présenté dans l’exemple précédent, il suffit souvent d’appliquer plusieurs fois le théorème de Millman pour obtenir

les grandeurs recherchées. Peu d’équations seront générées avec, par conséquent,

moins de risque d’erreur de calculs.

• Si c’est un courant qui est recherché, par exemple dans une résistance, penser à utiliser

le théorème de Millman pour trouver d’abord la tension aux bornes de cette résistance.

Chapitre 1

© Dunod. Toute reproduction non autorisée est un délit.

E1

E

0

10 5

+

+ 2

+

R1 R3 R2

10 5

VA =

=

= 5,, 7 V

1

1

1

1

1

1

+

+

+

+

R1 R3 R2

10 20 5

13

9782100847914-Livre.indb 13

27/11/22 16:01

fiche

7

Les ponts diviseurs

1. Le pont diviseur de tension

Le circuit de la figure 7.1 représente un pont de deux résistances placées en série et

alimentées par un générateur de tension parfait. Les deux résistances sont ainsi parcourues par le même courant.

I

R1

A

E

R2 VA

Figure 7.1

On s’intéresse au potentiel VA au point A, point commun aux deux résistances R1 et R2 ,

autrement dit, à la tension aux bornes de R2 .

E

Par simple application de la loi d’Ohm, on peut écrire : I =

.

R1 + R2

R2

E.

D’où : VA =

R1 + R2

Le principe du pont diviseur de tension

Le potentiel au point commun de deux résistances est égal à la tension qui règne aux

bornes de l’ensemble multiplié par la résistance connectée au potentiel le plus bas et

divisé par la somme des deux résistances.

Le potentiel au point A est donc égal à une fraction de la tension E, d’où la dénomination de pont diviseur de tension.

Important

Le principe du pont diviseur de tension ne peut s’appliquer que si les deux résistances

sont parcourues par le même courant.

14

9782100847914-Livre.indb 14

27/11/22 16:01

2. Le pont diviseur de courant

I2

R1

R2

U

QCM

I

I1

Fiche 7

Le circuit de la figure 7.2 représente un pont de deux résistances placées en parallèle et

alimentées par un générateur de courant parfait. Les trois dipôles sont ainsi soumis à la

même différence de potentiel U.

Figure 7.2

U =

Exercices

On s’intéresse aux valeurs des deux courants I1 et I 2 qui parcourent respectivement les

deux résistances R1 et R2 .

Si on considère que la source de courant alimente l’association en parallèle des deux

résistances, on obtient, par une simple application de la loi d’Ohm :

R1 R2

I.

R1 + R2

Par conséquent :

R2

ÏI = U =

I

ÔÔ 1 R1

R1 + R2

Ì

R1

ÔI2 = U =

I

ÔÓ

R2

R1 + R2

Le principe du pont diviseur de courant

Les principes du pont diviseur de tension ou de courant sont a priori très simples mais

restent d’une utilité capitale dans bon nombre d’applications. Ils permettent en effet

d’avoir un accès immédiat à une grandeur électrique donnée en faisant le minimum de

calculs.

Il convient toutefois de bien retenir les conditions dans lesquelles s’appliquent ces principes, en particulier le fait que le diviseur de tension est caractérisé par la circulation du

même courant dans les deux résistances.

Chapitre 1

© Dunod. Toute reproduction non autorisée est un délit.

Lorsqu’une source de courant I alimente deux résistances associées en parallèle,

chacune des résistances est parcourue par le courant I multiplié par la valeur de l’autre

résistance et divisé par la somme des deux.

15

9782100847914-Livre.indb 15

27/11/22 16:02

fiche

Le principe de superposition

8

Dans un circuit linéaire possédant plusieurs générateurs de tension, et à condition que

ces sources soient indépendantes, tout potentiel en un point quelconque (ou tout courant

dans une branche du circuit) est égal à la somme des potentiels (ou des courants) créés

séparément par chaque générateur, les autres générateurs étant éteints, c’est-à-dire courtcircuités. Si le circuit contient des générateurs de courant, le principe reste valable si les

sources sont indépendantes : on effectue les calculs avec chaque source prise séparément

en remplaçant les générateurs de courant par des circuits ouverts.

Le principe de superposition étant une conséquence directe de la linéarité des composants du circuit, il est généralisable à tout régime de fonctionnement et à tout circuit

contenant uniquement des composants linéaires. Dès lors qu’un circuit contient des

éléments non linéaires, par exemple des diodes, ce principe ne peut plus s’appliquer. Il

ne s’applique pas non plus au calcul des puissances.

Exemple

Dans le circuit de la figure 8.1, on cherche à calculer le courant I dans la résistance R3.

I

R1 = 10 Ω

R2 = 5 Ω

I0 = 0,1A

E1 = 10V

E 2 = 20V

Figure 8.1

D’après le principe de superposition, ce courant est la somme de trois courants I1, I 2 et

I 3 correspondant respectivement aux contributions de chaque générateur E1, E2 et I 0. On

calcule alors successivement chaque courant en ne laissant subsister, à chaque fois, qu’un

seul des trois générateurs. Avec E1 seul, (figure 8.2), on a :

I1 =

E1

10

=

= 0, 66 A.

R1 + R2 15

Pour calculer I 2, il suffit de court-circuiter E1, de laisser I 0 éteinte (en circuit ouvert) et de

« rallumer » E2 pour obtenir :

E2

20

I2 = == -1, 33 A.

R1 + R2

15

16

9782100847914-Livre.indb 16

27/11/22 16:02

R1 = 10 Ω

Fiche 8

I1

R2 = 5 Ω

E1 = 10V

Figure 8.2

I3 =

QCM

Pour le calcul de I 3 (figure 8.3), le circuit est un simple pont diviseur de courant :

R1

I 0 = 0, 066 A.

R1 + R2

I3

R1 = 10 Ω

Exercices

R2 = 5 Ω

I0 = 0,1A

Figure 8.3

Au final, on fait la somme algébrique des trois courants calculés indépendamment :

I = I1 + I 2 + I 3 = 0, 66 - 1, 33 + 0, 066 = -0, 6 A.

Rappel

Le principe de superposition ne s’applique pas aux puissances électriques. Cela signifie

que la puissance consommée par un dipôle n’est pas égale à la somme des puissances Fiches 13, 14

qu’il consomme en provenance de chacun des générateurs. En effet, la puissance étant

le produit de la tension et du courant, ce n’est pas une forme linéaire. Or, le principe de

superposition est une conséquence directe de la linéarité des circuits.

On pourra utiliser le principe de superposition pour déterminer courants et tensions

dans les dipôles qui nous intéressent mais on ne fera le calcul des puissances qu’à la fin,

une fois reconstituées les grandeurs électriques totales.

D’une manière générale, le principe de superposition ne s’applique pas non plus en

Chapitre 3

présence de dipôles non linéaires (diode par exemple).

Chapitre 1

© Dunod. Toute reproduction non autorisée est un délit.

Lorsqu’on annule un générateur de tension, on le court-circuite, et lorsqu’on annule un

générateur de courant, on le remplace par un circuit ouvert.

17

9782100847914-Livre.indb 17

27/11/22 16:02

fiche

9

Les théorèmes de Thévenin et Norton

Les théorèmes de Thévenin et de Norton sont sans doute les théorèmes les plus puissants et les plus importants de l’électrocinétique. Leur maîtrise permet bien souvent de

résoudre des problèmes complexes en un minimum de temps et en manipulant très peu

d’équation.

3. Le théorème de Thévenin

En régime continu, tout réseau linéaire dipolaire est équivalent à un générateur de tension

dit de Thévenin, de force électromotrice E0 et de résistance interne r (figure 9.1).

La résistance r est égale à la résistance équivalente du réseau lorsque tous ses générateurs sont éteints.

La tension E0 est égale à la tension à vide du réseau (lorsque I = 0 dans le circuit de

la figure 9.1).

I

I

r

U

U = E0 − rI

⇔

E0

U = E0 si I = 0

(tension à vide)

Figure 9.1

Remarque

Puisqu’il s’agit de déterminer un générateur de tension équivalent à un dipôle, nous

employons bien évidemment la convention générateur.

4. Le théorème de Norton

Le théorème de Norton propose un autre dipôle simple équivalent à tout réseau dipolaire.

En régime continu, tout réseau linéaire dipolaire est équivalent à un générateur de

courant dit de Norton, de courant I et de résistance interne r (figure 9.2) égale à la

résistance interne du générateur de Thévenin.

La résistance r est égale à la résistance équivalente du réseau lorsque tous ses générateurs sont éteints.

On utilise volontiers le terme de conductance interne g pour qualifier 1 / r .

18

9782100847914-Livre.indb 18

27/11/22 16:02

Fiche 9

Le courant I est égal au courant de court-circuit du dipôle (courant circulant dans le

dipôle lorsque l’on court-circuite ses deux bornes).

I = I0 si U = 0

I

I = I0 + U / r

⇔

I0

r

U

QCM

U

(court-circuit)

Figure 9.2

Exercices

5. L’équivalence Thévenin – Norton

Un générateur de tension de Thévenin, de force électromotrice E et de résistance interne

E

r est équivalent à un générateur de Norton, de courant I 0 =

et de même résistance

R

interne r (figure 9.3).

r

⇔

I0 = E / r

r

E

Les théorèmes de Thévenin et de Norton sont utiles lorsque l’on recherche une grandeur électrique particulière, par exemple le courant dans une résistance placée dans un

circuit complexe. On considère alors que cette résistance est alimentée par le reste du

circuit que l’on isole ainsi et dont on cherche l’équivalent de Thévenin ou de Norton.

Pour ce faire, on peut invoquer directement l’un des deux théorèmes ou encore effectuer des transformations Thévenin – Norton et Norton – Thévenin successives jusqu’à

réduire le circuit à sa plus simple expression.

Chapitre 1

© Dunod. Toute reproduction non autorisée est un délit.

Figure 9.3

19

9782100847914-Livre.indb 19

27/11/22 16:02

fiche

10

Les circuits linéaires en régime

sinusoïdal

Le régime sinusoïdal constitue, après le régime continu, le régime électrique le plus

couramment utilisé. Les électriciens ont introduit des modèles théoriques très intéressants qui permettent d’utiliser en régime sinusoïdal les mêmes lois et théorèmes qu’en

régime continu. Ce chapitre est consacré à une première approche simple grâce à laquelle

nous allons introduire la notion d’impédance réelle et celle de valeur efficace, deux

concepts essentiels en électronique.

1. Définitions et principes fondamentaux

L’étude des circuits linéaires en régime sinusoïdal correspond à l’étude des réseaux

électriques composés uniquement d’éléments linéaires (résistances, condensateurs et

auto-inductances, notamment), alimentés par des sources de tension ou de courant sinusoïdales. Pour une source de tension, on considérera en général :

e(t ) = E0 cos wt

Très souvent, on parle également de signal sinusoïdal.

La tension E 0 représente l’amplitude de la tension sinusoïdale (en volts), w est sa

pulsation en radians par seconde. On définit à partir de ces grandeurs, les paramètres

suivants :

w

f =

: fréquence du signal en hertz (Hz)

2p

T =

Fiche 4

1 2p

=

: période en secondes.

f

w

Le régime sinusoïdal fait partie (avec le régime continu) des régimes permanents (par

opposition aux régimes variables ou transitoires).

Pour diverses raisons, l’énergie électrique est fournie sous la forme d’un signal sinusoïdal. Ceci confère à l’étude des circuits en régime sinusoïdal un intérêt primordial.

Propriété fondamentale

Dans un circuit linéaire fonctionnant en régime sinusoïdal, tous les courants et toutes

les tensions dans le circuit sont sinusoïdaux, de même pulsation que la source d’alimentation du circuit.

Ces grandeurs électriques possèdent des amplitudes qui dépendent bien évidemment

des éléments du circuit, mais aussi de la pulsation w de la source. De plus, toutes ces grandeurs présentent la plupart du temps des déphasages par rapport à la source principale.

20

9782100847914-Livre.indb 20

27/11/22 16:02

Fiche 10

Par conséquent, si on considère un courant i (t ) ou une tension v (t ) quelconque dans le

circuit, on peut écrire :

i (t ) = I1 cos(wt + j1 ) et v (t ) = V2 cos(wt + j 2 ).

Exercices

QCM

Les paramètres j1 et j 2 sont respectivement les déphasages de i (t ) et de v (t ) par

rapport à la source e(t ). Pour être plus précis, il faut les appeler « avances algébriques

de phase » puisqu’ils sont comptés positivement. Lorsqu’un déphasage est négatif, il

traduit donc un retard de phase. Lorsque deux signaux présentent un déphasage de p/2,

ils sont dits en quadrature de phase. S’ils sont déphasés de p, ils sont dits en opposition

de phase. I1 est l’amplitude du courant sinusoïdal i (t ). V2 est l’amplitude de la tension

sinusoïdale v (t ). j1, j 2, I1 et V2 dépendent de E0 et des valeurs des différents éléments

du circuit, mais également de la pulsation w.

Pour des raisons qui seront explicitées plus loin, on introduit, pour les grandeurs sinusoïdales, la notion de valeur efficace. On pose e(t ) = E0 cos wt = Eeff 2 cos wt . De

même, on a : i (t ) = I eff 2 cos(wt + j1 ) et v (t ) = Veff 2 cos(wt + j 2 ). Les paramètres

Eeff , I eff et Veff sont appelées valeurs efficaces, respectivement de e(t ), i (t ) et v (t ).

2. La notion d’impédance

Lorsqu’un dipôle passif est alimenté par une source de tension sinusoïdale e(t ), il est

parcouru par un courant i (t ) sinusoïdal dont l’amplitude I 0 peut être déterminée par

l’équation :

E0 = Z ◊ I 0 ou encore Eeff = Z ◊ I eff

où Z représente l’impédance (exprimée en W) du dipôle. Cette équation traduit le fait

que la loi d'Ohm s'applique en régime sinusoïdal à condition de considérer les amplitudes des grandeurs électriques. Pour les dipôles usuels, les valeurs des impédances

sont résumées sur la figure 10.1. On remarquera que ces impédances dépendent de la

pulsation de la source e(t ), ce qui corrobore bien le fait que les amplitudes des courants

et tensions dans un circuit en régime sinusoïdal dépendent de la pulsation de la source

d'alimentation.

Z= R

C

L

Z = Lω

Z=

1

Cω

Chapitre 1

© Dunod. Toute reproduction non autorisée est un délit.

R

Figure 10.1

21

9782100847914-Livre.indb 21

27/11/22 16:02

fiche

11

Fiche 10

Le modèle complexe en régime

sinusoïdal

Dès lors que les circuits étudiés comportent plusieurs dipôles, la notion simple d’impédance ne suffit plus. On a alors recours à une méthode plus puissante qui fait appel à la

transposition pure et simple du circuit réel en un modèle théorique basé sur les nombres

complexes.

1. Les notations

En considérant une grandeur électrique sinusoïdale u(t ), on peut écrire :

u(t ) = Ueff 2 cos (wt + j )

u(t ) = ¬ [Ueff 2 cos (wt + j ) + jUeff 2 sin (wt + j ) ] = ¬ [Ueff 2e j (wt +j ) ]

On transpose alors la plupart du temps le schéma réel du circuit sous la forme d’un

modèle dit complexe, dans lequel les grandeurs sont remplacées par leurs formes

complexes notées U . Cette forme complexe est issue de l’association, à la grandeur électrique réelle u(t ), de la fonction complexe Ueff 2e jwt .

Comme, dans un circuit, toutes les grandeurs sont sinusoïdales de même pulsation

que la source et que chacune de ces grandeurs possède une valeur efficace, on retiendra

l’association suivante :

u(t ) Æ U = Ueff e jj .

Dans ce modèle (qui n’est rien d’autre qu’une représentation théorique du circuit), tout

dipôle linéaire possède une impédance dite complexe Z = R + jX où R représente sa

résistance et X sa réactance. Le module de Z, noté Z correspond à l’impédance réelle

telle qu’elle est décrite dans le paragraphe précédent.

On a :

Z = Z € Z = Ze jarg( Z )

La figure 11.1 présente les valeurs des impédances complexes des trois dipôles passifs

usuels.

R

Z= R

C

L

Z = jLω

Z=

1

jCω

Figure 11.1

22

9782100847914-Livre.indb 22

27/11/22 16:02

2. La représentation de Fresnel

M

Z

y

0

( Z = R+ jX )

X

QCM

Im

Fiche 11

En représentant le nombre complexe Z = R + jX dans le plan complexe, on obtient le

diagramme dit de Fresnel (figure 11.2) qui permet d’obtenir un certain nombre de relations très utiles.

Re

R

Figure 11.2

X

et Z = R 2 + X 2

R

R

R

X

cosy =

=

=

et sin y =

2

2

Z

Z

R +X

Exercices

Soit : y = arg Z

On a : tan y =

X

R2 + X 2

.

Dans le modèle complexe, tout courant i(t) ou tension u(t) dans le circuit possède une

représentation complexe I ou U qui peut s’écrire sous la forme :

I = I eff e jj1 avec I eff = I : valeur efficace de i (t )

et :

j1 = arg( I ) : déphasage de i (t ) par rapport à e(t)).

ou encore :

U = Ueff e jj 2 avec Ueff = U : valeur efficace de u(t )

et :

j 2 = arg(U ) : déphasage de u(t ) par rapport à e(t)).

i (t ) = I eff 2 cos(wt + j1 ) Æ I = I eff e jj1

u(t ) = Ueff 2 cos(wt + j 2 ) Æ U = Ueff e jj 2 .

Il suffit par conséquent de rechercher les modules et arguments des grandeurs complexes

associées aux grandeurs électriques pour caractériser entièrement ces dernières. C’est là

tout l’intérêt de cette représentation complexe qui nous permet d’entrevoir une méthode

générale pour résoudre n’importe quel problème en régime sinusoïdal.

Chapitre 1

© Dunod. Toute reproduction non autorisée est un délit.

Autrement dit, chaque grandeur électrique du circuit (courant ou tension), possède une

représentation complexe définie par :

Fiche 12

23

9782100847914-Livre.indb 23

27/11/22 16:02

fiche

12 Le régime sinusoïdal – Méthode

1. La transposition au modèle complexe

En règle générale, l’étude d’un circuit en régime sinusoïdal consiste à identifier les

expressions de grandeurs électriques, courants ou tensions, dans un montage alimenté

par une source sinusoïdale, par exemple e(t ) = Eeff 2 cos wt .

Exemple

Dans le circuit représenté sur la figure 12.1.a, on cherche à déterminer l’expression de u(t).

1

jCω

C

A

e (t)

→

A

E = Eeff

u(t )

R

R

a

U

b

Figure 12.1

On transpose immédiatement le schéma dans sa représentation complexe (figure 12.1.b) et

on y applique le principe du pont diviseur de tension :

U =

R

1

R+

jCw

E =

jRCw

Eeff .

jRCw + 1

2. Le retour au modèle temporel

Nous savons déjà que la tension u(t) est sinusoïdale de même pulsation que e(t) puisque

le circuit est linéaire. Il nous faut donc trouver sa valeur efficace et son éventuel déphasage par rapport à e : u(t ) = Ueff 2 cos(wt + j ).

On a : U = Ueff e jj =

Soit : Ueff = U =

jRCw

Eeff .

jRCw + 1

RCw Eeff

1 + R 2C 2w 2

.

24

9782100847914-Livre.indb 24

27/11/22 16:02

Et :

Fiche 12

p

Ê jRCw

ˆ

j = argU = arg Á

Eeff ˜ = arg( jRCw ) - arg( jRCw + 1) = - arctan( RCw ).

jRC

w

+

2

1

Ë

¯

D’où : u(t ) = Ueff 2 cos (wt + j ).

RCw

R 2C 2w 2 + 1

(

cos wt +

)

p

- arctan( RCw ) .

2

QCM

Soit : u(t ) = Eeff 2

Important

Exercices

De même qu’il ne faut jamais oublier que le module d’un quotient est égal au quotient

des modules, il faut également se souvenir que l’argument d’un quotient est égal à la

différence entre l’argument du numérateur et celui du dénominateur.

Le lecteur devra également se souvenir des propriétés suivantes :

b

pour a > 0

a

b

arg(a + jb) = arctan ± p pour a < 0

a

arg(a + jb) = arctan

Ce sont ces propriétés qui sont couramment utilisées pour calculer les modules et

arguments des nombres complexes en électrocinétique.

3. Le principe général

Dans la représentation complexe, en prenant soin de considérer l’impédance complexe

de chaque dipôle, les lois et théorèmes fondamentaux de l’électricité qui gouvernent les

circuits en régime continu restent valables en régime sinusoïdal : lois de Kirchhoff, théorème de Millman, principe de superposition, théorèmes de Thévenin et de Norton. Les

règles qui régissent les associations de dipôles sont également transposables au modèle

complexe.

Dans le schéma électrique transposé à sa représentation complexe, toutes les lois de

l’électricité valables pour le régime continu, s’appliquent aux grandeurs et variables

complexes.

Chapitre 1

© Dunod. Toute reproduction non autorisée est un délit.

Important

Si la méthode présentée ici est simple dans son principe, il n’en demeure pas moins

qu’elle exige une bonne maîtrise de la manipulation des nombres complexes. On trouvera en annexe, à la fin de cet ouvrage, un formulaire qui rassemble toutes les formules

utiles dans ce domaine, entre autres. Il est recommandé de s’exercer autant que de besoin

afin d’acquérir la maîtrise de la résolution des problèmes d’électrocinétique en régime

sinusoïdal.

25

9782100847914-Livre.indb 25

27/11/22 16:02

fiche

13 La puissance électrique

Au-delà des courants et tensions, la grandeur électrique qui revêt un caractère fondamental est la puissance électrique, directement liée au concept d’énergie. Bien souvent,

les systèmes électriques ont pour objet de transformer de l’énergie électrique en une autre

forme d’énergie (mécanique ou thermique par exemple). Les systèmes électroniques,

pour remplir leur fonction, consomment de l’énergie ou encore la dissipent sous forme

de chaleur. Le dimensionnement des générateurs qui vont alimenter les circuits dépend

essentiellement de la connaissance que nous avons de ces phénomènes.

1. La puissance instantanée

La puissance instantanée consommée par un dipôle électrique récepteur ou fournie par

un dipôle générateur (figure 13.1), quel que soit le régime de fonctionnement, est définie

par p(t ) = e(t )i (t ). Elle s’exprime en watts (W).

i(t )

i(t )

e (t )

e (t )

Figure 13.1

2. L’énergie dans un dipôle

La notion d’énergie ne correspond pas à une grandeur instantanée. Elle représente, en

quelque sorte, sur un intervalle de temps [ t1; t2 ] donné, la sommation de toutes les puissances instantanées. Ainsi, l’énergie, en joules (J) consommée par un dipôle récepteur

(ou délivrée par un générateur) sur un intervalle de temps [ t1; t2 ] est définie par :

t2

t2

t1

t1

E = Ú p(t ) dt = Ú e(t )i (t ) dt .

3. La puissance moyenne

La puissance moyenne consommée sur un intervalle de temps [ t1; t2 ] par un dipôle récepteur ou délivrée par un dipôle générateur est définie par :

t

E

1 2

P =

p(t ) dt =

.

Ú

t2 - t1 t

t2 - t1

1

Cette puissance moyenne s’exprime, comme la puissance instantanée, en watts. La

puissance moyenne consommée sur une durée infinie (de -• à +•) se calcule ainsi :

T

1

Ú e(t )i(t ) dt .

T Æ• 2T

-T

P = lim

26

9782100847914-Livre.indb 26

27/11/22 16:02

Fiche 13

Pour le calcul de la puissance moyenne consommée entre les instants 0 et +•, on

utilisera l’expression :

T

1

P = lim Ú e(t )i (t ) dt .

T Æ• T

0

4. Le principe de la conservation de l’énergie

QCM

Dans un circuit électrique formé de n dipôles récepteurs et de p dipôles générateurs, quel

que soit le régime de fonctionnement, la somme des puissances fournies par l’ensemble

des générateurs est égale à la somme des puissances consommées par l’ensemble des

dipôles récepteurs.

5. La puissance en régime continu

Exercices

Un circuit linéaire en régime continu ne comporte en général que des générateurs de

tension ou de courant et des résistances. Dans ce régime de fonctionnement, les tensions

et courants dans tout le circuit sont constants.

Ainsi, la puissance instantanée consommée par une résistance en régime continu

(figure 13.2) est constante et égale à sa valeur moyenne :

p(t ) = UI = C te = P .

Comme I =

U

U2

= RI 2.

, on a : p(t ) = P =

R

R

R

I

U

Figure 13.2

Dans un circuit alimenté par plusieurs générateurs, le principe de superposition ne

s’applique pas au calcul des puissances ou des énergies mises en jeu. Ainsi, il n’est pas

possible de considérer que la puissance consommée par un dipôle est la somme des

puissances qu’il consommerait si le circuit était alimenté par chaque générateur pris

indépendamment. On utilise le principe de superposition pour calculer les courants et

les tensions et on calcule ensuite les puissances à partir de ces grandeurs.

Chapitre 1

© Dunod. Toute reproduction non autorisée est un délit.

Attention

27

9782100847914-Livre.indb 27

27/11/22 16:02

fiche

14 La puissance en régime sinusoïdal

En régime sinusoïdal, la notion de puissance est quelque peu particulière. En effet, les

différents dipôles linéaires que nous avons côtoyés jusqu’à présent ne se comportent

pas de la même manière : si les résistances consomment effectivement de l’énergie et la

dissipent sous forme de chaleur, les condensateurs et le bobines ne font qu’emmagasiner

temporairement de l’énergie électrique pour la restituer ensuite sous la même forme. Cela

va nous conduire à un modèle de puissance compatible avec la représentation complexe.

1. La valeur efficace d’un signal sinusoïdal

Une tension sinusoïdale d’expression e(t ) = E0 cos wt , débitant dans une résistance R

(figure 14.1), délivre une puissance instantanée :

T

p(t ) =

( E0 cos wt )2

E2

1 ( E cos wt )2

dt = 0 .

, soit la puissance moyenne : P = Ú 0

R

T0

R

2R

R

i( t) = Ieff 2 cos( wt + j)

e(t ) = Eeff 2 cos wt

Figure 14.1

La source de tension continue qui délivrerait la même puissance moyenne aurait pour

E