A Phased Calculation Method of Switching Loss of

SiC MOSFET Based on High Power Conditions

Zhi Zheng

School of Electrical Engineering

Xi'an Jiaotong University

Xi’an, China

Yijun Wang

School of Electrical Engineering

Xi'an Jiaotong University

Xi’an, China

Feng Wang

School of Electrical Engineering

Xi'an Jiaotong University

Xi’an, China

Fang Zhuo

School of Electrical Engineering

Xi'an Jiaotong University

Xi’an, China

Abstract—As an emerging wide-bandgap semiconductor

device, SiC MOSFET provides the advantages of high frequency,

high efficiency and high power density for power electronic

devices due to its excellent performance. As an important factor

to study the switching performance of devices, switching loss is of

great significance to its accurate calculation. This paper firstly

analyzes the turn-on and turn-off processes of SiC MOSFETs,

subdivides them into ten stages, and obtains the calculation

method of switching losses in each stage. Then the corresponding

switching loss value is obtained through simulation and

experiment. Finally, the loss value calculated by the proposed

calculation method is compared with the simulation and

experiment, which verifies the high accuracy of the loss

calculation method.

Keywords—SiC MOSFET, switching loss, wide bandgap devices

I. INTRODUCTION

In recent years, power semiconductor devices have

developed from low-power, low-frequency and semi-controlled

to high-power, high-frequency and fully-controlled. As a

representative of wide band gap devices, SiC MOSFET is

applied more frequently in various power electronic devices

because of its various advantages including high voltage

resistance, high temperature resistance and fast switching. It is

widely used in various topologies in high-power scenarios [1],

[2]. The loss modeling and calculation of switching devices has

always been an important part in the evaluation and analysis of

power electronic systems. It is of great significance to the

efficiency prediction and parameter optimization of power

electronic system. But at the same time, the high switching

frequency and complex switching process make the switching

loss analysis of SiC MOSFET more complex [3], [4].

The switching loss of SiC MOSFET can be roughly

calculated through the integration of drain-source voltage and

drain current and switching time. This method is relatively

simple, but the accuracy is not high [5]. Based on the

simplified principle of charge conservation and flux

conservation in the switching process, the SiC MOSFET data

sheet can clearly track the influence of the change of a

parameter on the switching loss while avoiding complex

calculation [6]. Parasitic capacitance and parasitic inductance

are important influencing parameters when modeling the

switch [7], [8]. By considering the switching loss modeling of

parasitic capacitance and parasitic inductance as well as

experimental comparison, the relationship between switching

loss and parasitic parameters can be more accurately illustrated

[9], [10]. Calorimetry is based on relatively slow temperature

measurement and does not rely on the measurement of fast

switching conversion of voltage and current. It can be used to

accurately determine a single loss component, but it heeds high

experimental requirements [11]. Phased switch modeling loss

analysis can be used to accurately determine the loss value of

each stage, but most of the experimental verification is limited

to low-power scenarios [12].

In view of the advantages and disadvantages of the above

methods, this paper proposes a phased calculation method of

SiC MOSFET switching loss under high power conditions. The

switching process of SiC MOSFET is divided into ten stages,

and the parameters of each stage are modeled and analyzed in

detail by using the switching characteristics and considering the

influence of parasitic parameters in the circuit. On this basis,

the actual switching loss of SiC MOSFET can be calculated by

substituting the device parameters and electrical parameters

under actual working conditions. In order to verify the

reliability of the proposed method under high power density

conditions, the Ltspice simulation results and the experimental

results of dual-pulse test platform under high power density

conditions are compared and analyzed respectively, which

verifies the accuracy of the proposed calculation method.

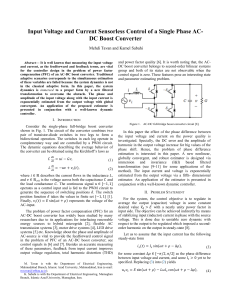

II. OPENING PROCESS MODELING AND LOSS ANALYSIS

Silicon carbide power device is a voltage-controlled device

and acknowledging its switching characteristics is of great

significance to analyze its switching loss. In most power

electronics applications, the switching process of silicon

carbide power devices can be described by diode clamped buck

circuit based on inductive load. In this paper, the driven lower

tube in the half bridge is used as the switch tube, and the upper

tube in the off state is equivalent to a diode. Its equivalent

circuit is shown in Fig. 1. Among them, this paper will take it

as the basis for studying the phased calculation method of SiC

MOSFET switching loss under high power conditions.

Fig. 2 shows the turning on process curve of SiC MOSFET.

The turn-on process can be divided into five states according to

the gate-source voltage and the state of the device: opening

delay stage, the current rise stage, the rapid voltage drop stage,

the slow voltage drop stage and the grid charging stage. The

circuit equivalent diagram of each stage is shown in Fig. 3.

This work was supported by the Shaanxi Province Key Research and

Development Program Project: Design and Simulation of Medium and Low

Voltage DC Power Distribution Multi-Port Converters for Distributed Energy

(2019ZDLGY18

-

09).

170

2022 The 4th International Conference on Power and Energy Technology

978-1-6654-8079-6/22/$31.00 ©2022 IEEE

2022 4th International Conference on Power and Energy Technology (ICPET) | 978-1-6654-8079-6/22/$31.00 ©2022 IEEE | DOI: 10.1109/ICPET55165.2022.9918410

Authorized licensed use limited to: UNIVERSITE DE SOUSSE. Downloaded on December 04,2023 at 05:09:20 UTC from IEEE Xplore. Restrictions apply.

on

V

g

R

g

L

DC

V

D

L

S

L

g

gd

C

gs

C

ds

C

d

s

loop

L

off

V

load

L

Fig. 1. SiC MOSFET half-bridge circuit with inductive load.

Fig. 2. SiC MOSFET turn-on process curve.

d

L

g

L

s

L

gd

C

gs

C

ds

C

d

i

d

s

onR

offR

loop

L

on

V

off

V

dc

V

load

I

on

V

d

L

g

L

s

L

gd

C

gs

C

ds

C

d

i

d

s

onR

offR

loop

L

dc

V

off

V

load

I

(a) (b)

d

L

g

L

s

L

gd

C

gs

C

ds

C

d

i

d

s

d

i

s

i

g

i

dc

V

loop

L

on

V

off

V

load

I

(c) (d)

(e)

Fig. 3 Circuit equivalent diagram in open phase: (a) Opening delay stage(T0-T1)

(b) Current rise phase(T1-T2) (c) Rapid voltage drop stage(T2-T3) (d) Voltage

slow drop stage (T3-T4) (e) Gate charging stage (T4-)

A. Opening delay stage (T0-T1)

At T0, the opening signal comes, and the driver output

voltage changes from negative pressure Voff to positive Von.

The drive circuit starts to charge the gate capacitor of SiC

MOSFET through the drive current Ig until reaching the gate

threshold voltage. At this time, the silicon carbide MOSFET is

in the off state and the DC bus voltage VDC remains unchanged,

so the value of capacitance Cgs and Cgd remains unchanged and

the voltage change rate on both capacitor is the same, we can

get (1)

gs

on gs G iss

dv

V v R C dt

=+

(1)

At T1, VGS reaches the SiC MOSFET gate threshold voltage

Vgs,th of. The time from T0 to T1 is recorded as the opening

delay time t1, which is (2)

1,

ln on off

g iss on gs th

VV

t R C VV

−

=−

(2)

Since the drain current does not flow through SiC

MOSFET channel, there is no loss at this stage.

10E=

(3)

B. Current Rise Phase (T1-T2)

At this time, the gate channel of the power module is on,

and the current flowing through it increases with the increase of

the driving voltage. At this stage, when the gate source voltage

vgs exceeds the threshold voltage Vgs, th, a conductive path will

be generated inside the SiC MOSFET to make the drain current

flow.

Same as the previous stage, in this stage vGS is still rising

exponentially, so id and the change rate of id can be obtained

,

( ) (1 )

G iss

t

RC

d m gs gs th m on

i g v V g V e−

− = −

(4)

At T2, when the drain current id reaches the peak, vGS

reaches the Miller platform voltage Vmiller, which is determined

by the load current, switch transconductance and grid threshold

voltage:

,

load

miller gs th

m

I

VV

g

=+

(5)

The time (t2) required for the drain current to increase from

zero to the load current can be calculated as

21miller

G iss on

V

t R C ln V

− −

(6)

The switching loss is

2

20

() 1

g iss G iss

tt

tt RC RC

m on d s

dc m on

tG iss

g V L L

E V e g V e dt

RC

−−

=

=

+

= − −

(7)

171

Authorized licensed use limited to: UNIVERSITE DE SOUSSE. Downloaded on December 04,2023 at 05:09:20 UTC from IEEE Xplore. Restrictions apply.

C. Rapid Voltage Drop Stage (T2-T3)

At T2, the drain current id reaches the peak and the drain

source current vds begins to drop rapidly. At this stage, Ig only

charges the capacitor Cgd while vgs remains constant, which is

called Miller platform. Since the change rate of vds at this stage

is much higher than that of vGS, it can be obtained that

gd g

ds

gd

dv i

dv

dt dt C

= − = −

(8)

Drain-source voltage change rate is mainly affected by the

gate current ig and the parasitic capacitance Cgd according to

the formula above. Due to the great influence of gate-drain

capacitor Cgd showed during Miller platform, it is also called

Miller capacitor. Cgd is a function of vds, and when vDS is low,

Cgd increases significantly as vDS decreases. At higher vDS, the

Miller capacitance Cgd is almost constant. In the stage of rapid

voltage decline, Cgd almost remains constant, and its average

value Cgd,av can be estimated as constants. Therefore, the drain

voltage decreases linearly, and the following equation can be

obtained:

( )

,

on miller

ds dc g gd av

V V t

vV RC

−

=−

(9)

t3 can be obtained:

( )

( )

,

3,

dc miller gs th

g gd av on miller

V V V

t R C VV

−−

=−

(10)

By assuming that VDS decreases linearly and ID is

approximately equal to Iload, the energy loss at this stage can be

obtained as

( ) ( ) ( )

3

30,

tt on miller

dc ds load

tg gd av

V V t

E V v I dt

RC

=

=

−

− −

(11)

D. Voltage Slow Drop Stage (T3-T4)

When the drain-source voltage VDS drops to VMiller-VGS, th,

SiC MOSFET starts to work in the ohms region, that is, the

voltage slow drop stage, at this time the Miller capacitor Cgd

almost remains unchanged. As shown in Fig. 3(d). The channel

voltage controlled current source is now replaced by an on-

state resistor, Rds,on. The grid-source voltage vgs remains at the

Miller voltage. Since the vgs remains in the Miller platform

region, the entire gate current will flow through the Cgd, so the

decline rate of the vds is approximated as a linear function using

the same method as in the rapid voltage drop phase.

( )

( )

,on miller

ds miller gs th g gd

V V t

v V V RC

−

= − −

(12)

The time of this phase is

( )

( )

( )

,,

4

miller gs th load ds on

g gd on miller

V V I R

t R C VV

−−

=−

(13)

At this phase

( )

42

4,

0

tt

load ds on

t

E I R dt

=

=

(14)

E. Gate Charging Stage (T4-)

The power module enters the variable resistance area from

the saturation area, and the gate driving circuit continues to

charge the gate capacitance. The grid-source voltage vgs breaks

through the Miller platform voltage Vmiller and finally rises to

Von, and the power module is fully opened.

At this stage, the time constant of this exponential rise

differs from that of the conduction current rise due to the larger

gate-drain capacity resulting from the high drain-source voltage.

The duration of this phase can be calculated as

51on miller

G iss on

VV

t R C ln V

−

= − −

(15)

At this phase

( )

52

5,

0

t

load ds on

t

E I R dt

=

(16)

The total opening loss is

1 2 3 4 5on

E E E E E E= + + + +

(17)

III. TURNING OFF PROCESS MODELING AND LOSS ANALYSIS

Fig. 4 shows the turning off process curve of SiC MOSFET.

According to the gate-source voltage and the state of the device,

the turn-on process can be divided into five states: shutdown

delay stage, slow voltage rise stage, rapid voltage rise stage,

current drop stage and gate discharge stage. Before T5, SiC

MOSFET is in completely conducting state. VGS is the driving

positive voltage Von and Ig is 0. IDS is the load current IL, VDS is

the conduction voltage drop VDS.

T5T6T7T8T9

0

Vgs Ig Id Vds

t

t

Vgs,Ig,Id,Vds

Vth

Vdc

Voff

Vmiller

Von

T10

Fig. 4. SiC MOSFET turning off process curve.

off

V

d

L

g

L

s

L

gd

C

gs

C

ds

C

d

i

d

s

dc

V

loop

L

on

V

load

I

offR

onR

d

L

g

L

s

L

gd

C

gs

C

ds

C

d

i

d

s

d

i

s

i

g

i

dc

V

loop

L

off

V

on

V

load

I

offR

onR

(a) (b)

172

Authorized licensed use limited to: UNIVERSITE DE SOUSSE. Downloaded on December 04,2023 at 05:09:20 UTC from IEEE Xplore. Restrictions apply.

d

L

g

L

s

L

gd

C

gs

C

ds

C

d

i

d

s

g

i

dc

V

loop

L

off

V

on

V

load

I

offR

onR

d

L

g

L

s

L

gd

C

gs

C

ds

C

d

i

d

s

g

i

dc

V

loop

L

off

V

on

V

load

I

offR

onR

(c) (d)

d

L

g

L

s

L

gd

C

gs

C

ds

C

d

i

d

s

g

i

dc

V

loop

L

off

V

on

V

load

I

offR

onR

(e)

Fig. 5. Circuit equivalent diagram of turn-off phase: (a) Shutdown delay stage

(T5-T6) (b) Slow voltage rise stage(T6-T7) (c) Rapid voltage rise stage (T7-T8)

(d) Current drop stage (T8-T9) (e) Gate discharge stage (T9-) :

A. Shutdown Delay Stage (T5-T6)

At T5, the turn-off signal comes, and the voltage output by

the driver changes from positive voltage Von to negative voltage

Voff. The driving circuit starts discharging the gate capacitor of

SiC MOSFET through the driving current Ig until reaching the

gate threshold voltage. The analysis method at this stage is

consistent with the opening process. The difference is that at

this time, the SiC MOSFET is in the on state, vds very small, so

the Miller capacitor Cgd is much larger than the value in the on

state, resulting in a larger turn-off delay time than the turn-on

delay time ton. The gate source voltage and turn off delay time

can be expressed as:

6off

G iss miller off

V

t R C ln VV

−

=−

−

(18)

This time can be considered as the turning off delay time

before the drain voltage begins to increase. The energy loss in

this stage is the same as the conduction power loss in the on

state.

2

6 , 6load ds on

E I R t=

(19)

B. Slow Voltage Rise Stage(T6-T7):

At T6, vgs drops to Miller platform voltage Vmiller, and SiC

MOSFET enters saturation zone. It can be seen that this stage is

similar to the decline stage of vds in the opening process, and vds

is affected by Ig and Cgd. During VDS increasing from IloadRds, on

to vds = Vmiller-Vgs,th, vds rises slowly, and the switch is

equivalent to on state resistance. vds and voltage rise time t7

equal:

,off miller

ds load ds on g gd

VV

v I R t

RC

−

−

(20)

( )

,

7

gs th miller g gd

off miller

V V R C

tVV

−

−

(21)

At this phase

( )

72

7,

0

tt

load ds on

t

E I R dt

=

=

(22)

C. Rapid Voltage Rise Stage (T7-T8)

At the stage when vds increases from VMiller-Vgs,th to busbar

voltage Vdc, vDS increases rapidly. The analysis method of vDS

and voltage rise time is consistent with the opening process.

,,

8

()

g gd av dc miller gs th

miller on

R C V V V

tVV

−+

=−

(23)

The loss is

( )

( )

7,

,

80

,

off miller

tt miller gs th

g gd av

t

m miller gs th

VV t V V

RC

E

g V V dt

=

=

−

− + −

=

−

(24)

D. Current Drop Stage (T8-T9)

At T8, Vds reaches the bus voltage Vdc, and the load current

IL flows to the diode of the upper tube. IDS descends rapidly,

and its descent rate is equal to that of the opening stage. The

higher current drop rate induces a positive voltage drop on the

parasitic inductor in phase with the bus voltage. When vds

reaches Vdc, the reverse diode of the upper SiC MOSFET starts

to conduct, so the Iload moves from the channel of the lower SiC

MOSFET to the reverse diode of the upper SiC MOSFET.

However, the device is still in the saturation region, and the

channel current of SiC MOSFET is the same as that of the open

stage. At this stage, the gate loop relation equation is

established by using the relationship between the current of

three channels and the gate voltage.

( )

( )

( )

,

m s G iss

t

g L R C

d m miller off m off gs th

i g V V e g V V

−+

− + −

(25)

( )

,

9gs th off

m s G iss miller off

VV

t g L R C ln VV

−

= − +

−

(26)

The loss is

( ) ( )

( )

( )

( )

( )

9

90

m s g iss

m s g iss

t

tt g L R C

m miller ss

dc s d

tm s g iss

t

g L R C

m miller ss m ss th

g V V

E V L L e

g L R C

g V V e g V V dt

−

=+

=

−+

−

= + +

+

− + −

(27)

E. Gate Discharge Stage (T9-) :

This stage is the same as the opening process analysis and

the loss is 0.

10 0E=

(28)

173

Authorized licensed use limited to: UNIVERSITE DE SOUSSE. Downloaded on December 04,2023 at 05:09:20 UTC from IEEE Xplore. Restrictions apply.

The total turn-off loss is

6 7 8 9 10off

E E E E E E= + + + +

(29)

IV. SIMULATION RESULTS AND EXPERIMENTAL ANALYSIS

SiC MOSFET half-bridge module packaging tends to

provide higher voltage resistance and lower circuit parasitic

parameters. To verify the reliability of the proposed phased

calculation method for switching loss of SiC MOSFET under

high power conditions, the ROHM 1700V

BSM250D17P2E004 power module is selected as the switch

tube for simulation and test.

Double pulse test is an important way to evaluate the

switching transient characteristics of one component, which

can accurately reflect the switching loss of SiC MOSFET. The

topology schematic diagram adopted in this paper is shown in

Fig. 1. In order to meet the actual working conditions of high-

power density, the bus dc voltage and load current should be as

large as possible, and the parasitic induction of bus and circuit

should be as small as possible. With overall consideration, the

main electrical parameters and their values of the dual-pulse

test platform in this paper are shown in Table I.

TABLE I. DOUBLE PULSE TEST MAIN ELECTRICAL PARAMETERS

Components or

electrical parameters

Model or

Description

Value of number

SiC MOSFET

BSM250D17P2004

1700V/250A

DC bus voltage Vdc

/

1200V

Load current Iload

/

130A

Load inductive Lload

Hollow coil

160uH

Gate stray inductance

Lg

/

3nH

Source stray

inductance Ls

/

13.3nH

Power loop inductance

Lloop

Busbar Inductance

20nH

Drive voltage

Positive/Negative

voltage

+19V/-4V

Drive resistance

Open/Close

4.7Ω/1Ω

Double pulse time

15-5-3us

According to the calculation methods in the second and

third sections, the parameters of the switch are substituted into

the corresponding formula, and the duration, voltage and

current of each time period can be calculated by MATLAB.

The switching loss of each stage can be calculated by using the

data MATLAB calculated. LTSpice simulation software

supports SPICE circuit language and can simulate and model

the switch at the device level. By importing the precise SPICE

model of C2M0025120D provided by Cree's official website

into LTSpice simulation software and building a double pulse

test circuit, the loss simulation image and loss in each stage of

the switching process of the switch can be obtained. The

simulation image is shown in Fig. 6.

Fig. 6. Switching process loss simulation.

According to the parameters in the above table, a double-

pulse test experimental platform under high power conditions is

built and the experimental waveforms in Fig. 7 were obtained,

in which channel 1 is the drain voltage waveform, channel 2 is

the drain current waveform, and the M channel is the real-time

power waveform.

Fig. 7. Experimental results of switching process.

The calculation method, simulation results and

experimental results proposed in this paper are shown in Fig. 8.

Switching loss comparationConsidering the opening process,

the experimental results in the first stage show that there is a

little loss, which is due to the small oscillation in the opening

process, but its value is very small, nearly equal to 0, so the

calculation method in this paper is still accurate. The turn-on

loss mainly occurs in the second and third stages, because the

voltage and current are at large values in these two stages. The

losses in stage 4 and stage 5 are small, and the drain source

voltage is very small. The duration of stage 5 is longer than that

of stage 4, so the loss is also slightly larger. As to the turn-off

process, corresponding to the turn-on process, it can be seen

that the losses in stage 6 and 7 are small, the losses in stage 8

and 9 are high, and there are small losses in stage 10. Because

the drive opening resistance selected in this paper is greater

than the drive closing resistance and the opening time is greater

than the closing time, the opening loss is about twice that of the

closing loss.

174

Authorized licensed use limited to: UNIVERSITE DE SOUSSE. Downloaded on December 04,2023 at 05:09:20 UTC from IEEE Xplore. Restrictions apply.

6

6

1

/

6

100%