VHDL

VHDLVHDL

VHDL

Compl

ComplCompl

Compléments

mentsments

ments

Machines d

Machines dMachines d

Machines d’états

tatstats

tats

2

Machines d’états

Principe de fonctionnement

LA machine d’état s’apparente àun automate ou un grafcet

Le système est dans un état stable ( équivalent d’une étape pour le grafcet)

Il

peut

évoluer vers un autre état du système en fonction des entrées ( réceptivité

VRAIE)

A chaque état correspond une/des sorties actives ( les actions associées aux

étapes)

La représentation graphique est un diagramme à

bulle

Ne pas oublier de faire un tableau àcôtépour

préciser les sorties en fonction de l’état

Contraintes de fonctionnement

Une machine d’état a besoin d’une horloge

(quartz, astable en externe ou PLL embarquée)

Une transition est activée lorsque

L’étape source est active

La réceptivitéest vrai (équation logique sur les

entrées

Un front d’horloge survient

3

Machines d’états

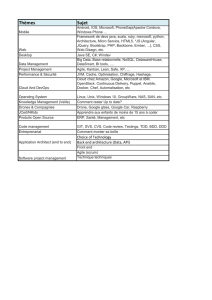

Les différentes types de Finite State

Machine (FSM)

Machine de Moore

La sortie ne dépend que de l’état

courant

Le temps de réaction dépend donc de

l’horloge

Cette machine peut-être qualifiée de

synchrone

Machine de Mealy

La sortie ne dépend de l’état courant

mais aussi des entrées

Le temps de réaction est plus rapide que

Moore

Cette machine peut-être qualifiée

d’asynchrone

Inconvénients: la durée minimum d’un

état n’ait plus garanti => L’état peut-être

interprétépar un autre système comme

un état parasite

4

Machines d’états

Codage des états

Création d’un type énuméré

Le compilateur affecte automatiquement un entier àchaque état

•T YPE etat IS (debut, etat1, etat2);

•SIGNAL etat_present : etat;

Codage àla main

L’utilisateur affecte un entier « à la main »

•Ex: début vaudra 0,état1 vaudra 1 et état 2 vaudra 2

SIGNAL etat_present : integer range 0 to 2;

OU

SIGNAL etat_present : std_logic_vector(1 down to 0);

Gestion des transitions

DANS UN PROCESS (car séquentiel)

Instructions CAS/IS bien adaptée

5

Machines d’états

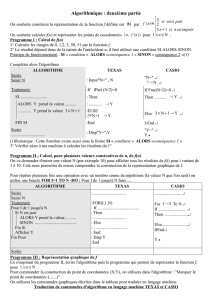

Exemple de codage à la main

Cahier des charges

la sortie S recopie l’état logique présent sur son

entrée E si celle-ci est restée stable après 2 coups

d’horloge successifs.

library ieee ; use ieee.std_logic_1164.ALL;

entity MAE is

port ( E,RST,HOR : in STD_LOGIC ;

S : out STD_LOGIC );

end MAE;

architecture COMPORTEMENT of MAE is

signal REG_ETAT : STD_LOGIC_VECTOR(2 downto 0);

process (HOR,RST)

begin

if RST='0' then REG_ETAT <= "000";

elsif (HOR’event and HOR='1') then

case REG_ETAT is

when "000" => S <= '0' ;

if E = '1' then REG_ETAT <= "001";

else REG_ETAT <= "000";

end if ;

when "001" => S <= '0' ;

if E = '1' then REG_ETAT <= "010";

else REG_ETAT <= "000";

end if ;

when "010" => S <= '0' ;

if E = '1' then REG_ETAT <= "011";

else REG_ETAT <= "000";

end if ;

when "011" => S <= '1' ;

if E = '1' then REG_ETAT <= "011";

else REG_ETAT <= "100";

end if ;

when "100" => S <= '1' ;

if E = '1' then REG_ETAT <= "011";

else REG_ETAT <= "101";

end if ;

when "101" => S <= '0' ;

if E = '1' then REG_ETAT <= "011";

else REG_ETAT <= "000";

end if ;

when others => REG_ETAT <= "00";

end case ;end if ;end process ;

end COMPORTEMENT ;

La sortie est

resynchronisée car

incluse dans le

process

6

6

7

7

8

8

9

9

1

/

9

100%