Cours DSP : Processeurs de traitement numérique de signal

Telechargé par

Omar Zamrani

Hicham Ghennioui

mailto:[email protected]

Université Sidi Mohamed Ben Abdellah

Faculté des Sciences et Techniques

Département de génie électrique

http://www.fst-usmba.ac.ma/departement-genie-electrique/

Retrouver tous les documents de Cours/TD/TP sur le site:

https://www.easyclass.com/

A.U. 2018-2019

Processeurs de traitement numérique de signal

DSP : Digital Signal Processor

PLAN

NGÉNÉRALITÉS SUR LES PROCESSEURS DE TRAITEMENT DE SIGNAL

nChaîne de traitement numérique de signal

nIntroduction aux processeurs de traitement de signal

NARCHITECTURE D’UN PROCESSEUR DSP

nArchitecture générale d’un DSP

nStructure interne du CPU

nUnité de génération d’adresse

nUnité de commande

nUnité de calcul

nUnité de mémorisation

NENVIRONNEMENT DE TRAVAIL

nInstallation de Hyperviseur VirtualBox et création d’une machine virtuelle

nCode Composer Studio 3.1

nDéveloppement pour un DSP

CHAPITRE 1 - GÉNÉRALITÉS SUR LES

PROCESSEURS DE TRAITEMENT DU

SIGNAL

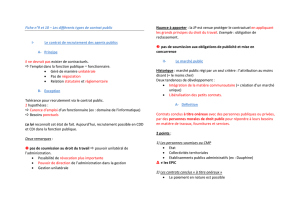

Conditionneur

Grandeur

physique

Cours DSP -Hicham Ghennioui 4

Signal original

Capteur

G

Convertisseur

Filtre anti-

repliement CAN

Echantillonneur

Quantification

Mémoires

DSP

Ports E/S

Calculs numériques

CNA Filtre de

lissage

Actionneur

Signal traité

Reconstruction

Numérisation

fs

CAN : Convertisseur Analogique

Numérique

Filtres anti-repliement et de lissage

sont des filtres passe-bas

CNA :

Convertisseur

Numérique

Analogique

DSP (Digital Signal Processor): c’est un

circuit intégré conçu pour des

manipulations de données à grande

vitesse. Il est le cœur de la chaîne de TNS.

CHAÎNE DE TNS À BASE DE DSP

nLecteur MP3 dictaphone

CHAÎNE DE TNS À BASE DE DSP - EXEMPLES

D’APPLICATION -

Source ti.com

§Les GPIO (General Purpose Input/Output) sont des ports d'entrée/sortie pour un usage

général

§I2S, également appelé Inter-IC Sound, Integrated Interchip Sound, ou IIS, un standard

d'interface électrique de type serial bus pour connecter des matériels audio numériques. Il est

principalement utilisé pour transporter des informations PCM entre le CD et le CNA dans un

lecteur de CD.

§Une liaison SPI (Serial Peripheral Interface) est un bus de données série synchrone qui opère

en mode Full-duplex. Les circuits communiquent selon un schéma maître-esclaves, où le maître

s'occupe totalement de la communication. Plusieurs esclaves peuvent coexister sur un même bus,

dans ce cas, la sélection du destinataire se fait par une ligne dédiée entre le maître et l'esclave

appelée Slave Select (SS).

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

61

61

62

62

63

63

64

64

65

65

66

66

67

67

68

68

1

/

68

100%