electronique b9 dsp ----- cours

mat_cours_dsp

I

Ed 2005

ELECTRONIQUE B9

DSP ----- COURS

CHAPITRE 1

INTRODUCTION

TRAITEMENT du SIGNAL

mat_cours_dsp

II

Ed 2005

1. INTRODUCTION 2

1.1. Digital Signal Processor (DSP) et microprocesseur (MPU) 2

1.2. Applications courantes des DSP 3

1.3. Produits existants 4

2. CHAINE DE TRAITEMENT DE SIGNAL EN NUMERIQUE 6

2.1. Eléments constitutifs 6

2.2. Echantillonnage et reconstitution 6

2.3. Numérisation et bruit de quantification 11

2.4. Traitement "en ligne" ou "au fil de l’eau …": vrai filtrage 12

2.5. Traitement par bloc simple buffer 12

2.6. Double Buffer et technique du « Pipe Line » 14

3. REPONSE IMPULSIONNELLE ET CONVOLUTION 15

3.1. Système linéaire 15

3.2. Réponse impulsionnelle (d'un système linéaire) 15

3.3. Construction de la réponse à une suite d’échantillons xn. Convolution

15

4. REPONSE EN FREQUENCE : FONCTION DE TRANSFERT 17

4.1. Etude générale avec x sinusoïdale, filtre de réponse impulsionnelle H 17

4.2. Gain pour f = 0 (donc pour le continu ) 18

5. FILTRES FIR, NON RECURSIFS REPONSE IMPULSIONNELLE FINIE 19

5.1. Description 19

5.2. Filtres à réponse impulsionnelle finie et filtres à phase linéaire ? 20

6. LE FILTRE FIR : « MOYENNEUR SIMPLE » 21

6.1. Etude théorique 21

6.2. Application N°1 : Filtre Moyenne mobile 22

6.3. Application N°2 : Valeur moyenne d'un signal 23

6.4. Application N° 3 : Elimination de parasites secteur (50Hz et ses

harmoniques), sur des mesures continues ou très basse fréquence 25

7. FILTRE IIR, RECURSIF REPONSE IMPULSIONNLLE INFINIE 26

7.1. Description 26

7.2. Avantage et inconvénient des IIR 26

7.3. filtre IIR de base du premier ordre, passe bas, moyenneur 27

7.4. Filtre IIR de base du second ordre 30

8. CORRELATION 33

9. FILTRES ADAPTATIFS 35

9.1. Principe 35

9.2. Algorithme du gradient 36

mat_cours_dsp

III

Ed 2005

CHAPITRE 2

MATERIEL

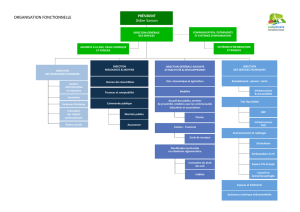

1. ARCHITECTURE GENERALE D'UN DSP 39

1.1. Architecture d'un microprocesseur standard 39

1.2. Architecture DSP: Harward 41

1.3. Conclusion sur l’architecture DSP 42

2. LE PROCESSEUR TEXAS VIRGULE FLOTTANTE TMS320C31 43

2.1. Synoptique général 43

2.2. Registres principaux 43

2.3. Les interruptions 44

3. GESTION DE LA MEMOIRE SUR TMS320C31 46

4. LE PIPE LINE DU C31 47

5. LE STARTER KIT C31 48

5.1. Schéma de principe 48

5.2. L’interface analogique TLC32040 49

5.3. Plan mémoire du STARTER KIT 56

mat_cours_dsp

IV

Ed 2005

CHAPITRE 3

LOGICIEL

1. ARITHMETIQUE BINAIRE ORIENTEE TRAITEMENT DE SIGNAL 58

1.1. Virgule fixe et virgule flottante 58

1.2. Acquisition et restitution par CAN et CNA 61

1.3. Introduction à la programmation en virgule fixe et en virgule flottante 64

2. LES LANGAGES DE PROGRAMMATION DES DSP: "C" OU

"ASSEMBLEUR" ? 66

2.1. Choix du langage 66

2.2. Principales difficultés du C sur DSP 67

3. RAPPEL SUR LES COMPILATEURS 68

4. L'ASSEMBLEUR DU DSP C31 69

4.1. Rappel des principaux registres de calcul 69

4.2. Format général d'une instruction assembleur 69

4.3. Types de données 69

4.4. Modes d’adressages 69

4.5. Directives d'assemblages 71

4.6. Instructions de base du C31 72

4.7. Temps d’exécution des instructions 76

5. UTILISATION DU LANGAGE C 77

5.1. Rappel de C ANSI standard 77

5.2. Le C sur un DSP Virgule fixe 85

5.3. Le C sur le DSP TMS320C31 virgule flottante 88

6. PROGRAMMATION EN C ET ASSEMBLEUR 91

6.1. Environnement "Runtime" du C sur C31 91

6.2. Instructions assembleur dans du C ? 94

6.3. Ecriture de fonctions C en assembleur 95

7. PROGRAMME DE DEMONSTRATION OUTILS DE TRAVAIL 99

7.1. Programme de démonstration sur Starter Kit 99

7.2. Les outils fournis 103

1

/

4

100%