JL Sanchez, Frédéric Morancho Patrick Austin, Marie Breil

État de l’art et évolution des dispositifs semiconducteurs de

puissance pour une meilleure gestion de l’énergie électrique

J-L Sanchez, Frédéric Morancho

LAAS-CNRS

Patrick Austin, Marie Breil,Abdelhakim Bourennane, Magali Brunet,

Karine Isoird,Henri Schneider

2

`Plan

•Introduction

•Composants de puissance unipolaires: MOSFETs

–Dispositifs conventionnels « limite du silicium »

–Nouveaux concepts : Superjonction et ilôts flottants

–Limites des performances de ces nouveaux composants

•Compoants MOS/bipolaires: IGBTs

–Nouvelles architectures

–IGBT « faibles pertes »

–Intégration IGBT-diode

–IGBT Bidirectionnels

–Limites des performances des IGBT

•Composants de puissance grand gap

–Propriétés des semiconducteurs grand gap

–Comparaison des limites des performances

–SiC, GaN, Diamant: tendances pour le futur

•Conclusion

3

•Introduction

•Composants de puissance unipolaires: MOSFETs

–Dispositifs conventionnels « limite du silicium »

–Nouveaux concepts : Superjonction et ilôts flottants

–Limites des performances de ces nouveaux composants

• Compoants MOS/bipolaires: IGBTs

–Nouvelles architectures

–IGBT « faibles pertes »

–Intégration IGBT-diode

–IGBT Bidirectionnels

–Limites des performances des IGBT

•Composants de puissance grand gap

–Propriétés des semiconducteurs grand gap

–Comparaison des limites des performances

–SiC, GaN, Diamant: tendances pour le futur

•Conclusion

Plan

4

Contexte

• Forte croissance de la demande d’énergie électrique.

• Aujourdhui l’énergie électrique représente 25% de la demande d’énergie finale et sa

croissance sera de 60% jusqu’à 2040.

•L’énergie électrique sera présente dans de nombreuses applications.

• Le marché des Semiconducteurs de puissance est estimé à 50 billions de dollars en 2010.

0

10

20

30

40

50

60

70

1980 2000 2020 2040

Power electrical consumption (Trillion kWh)

Population (Billion)

5

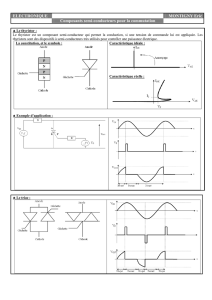

Electronique portable…automobile ..…transport ferroviaire

10

50

100 600 3500

HPM

IPMet ASIPM

Integration fonctionelle

applications industrielles

Applications industrielles

Traction ferroviare

Applications domestiques

et automobile)

Smart Power

(automobile

2

Micro

convertisseur

Equipement portables)

100

2500

I (A)

V (V)

1200

system integration

Domaines applicatifs

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

1

/

58

100%