Laboratoire 1 FETCH - HEIG-VD

Architecture des ordinateurs ARO2

Profs : C. Andrés Pena, R. Mosqueron

Assistants : Flavio Capitao, Anthony Convers, Alexandre Malki, Gaëtan Matthey

Laboratoire Microarchitecture FETCH

14/02/2017 – V2.0

- 1 -

Informations générales

Le laboratoire Microarchitecture dure 16 périodes et comprend 4 parties de 4 périodes chacune. Le

travail s’effectue par groupe de deux.

Le rapport à rendre portera sur deux laboratoires (8 périodes au total) :

1) le laboratoire Microarchitecture FETCH (4 périodes).

2) le laboratoire Microarchitecture DECODE (4 périodes).

Le rendu s’effectue sous forme de dossier compressé contenant le workspace complet (projets

Logisim, codes assembleur), et le rapport (.pdf) envoyé à l’assistant de votre groupe.

• Code partie FETCH et partie DECODE avec rapport à rendre avant :

o ARO2-1-A : le 29.03.2017, 23h59 à flavio.capitaocantante@heig-vd.ch

o ARO2-1-B : le 30.03.2017, 23h59 à gaetan.matthey@heig-vd.ch

o ARO2-1-C : le 28.03.2017, 23h59 à anthony.convers@heig-vd.ch

o ARO2-1-D : le 28.03.2017, 23h59 à alexandre.malki@heig-vd.ch

N’oubliez pas de sauvegarder et d’archiver votre projet à chaque séance de laboratoire

Objectifs du laboratoire

L’objectif principal est la réalisation simplifiée de la partie FETCH d’un processeur RISC avec

l’incrémentation du PC (Program Counter) et la lecture d’instructions. Vous apprendrez à assembler

un programme et à le charger dans la mémoire d’instruction. Ensuite, vous ajouterez un mécanisme

de saut et un mécanisme de gestion d’interruption.

Ce laboratoire est noté. Vous devez rendre les projets Logisim, les codes assembleur et un rapport.

Le rapport doit montrer votre compréhension de l’architecture du bloc FETCH, des instructions de

saut et des interruptions.

ARO2 – Architecture des Ordinateurs 2 - Laboratoire Microarchitecture FETCH

- 2 -

Outils

Pour ce laboratoire, vous devez utiliser les outils disponibles sur les machines de laboratoire

(A07/A09). Pour utiliser votre propre ordinateur portable, vous pouvez vous procurer une copie

allégée d’une machine de laboratoire sous forme d’une machine virtuelle. Elle est normalement

fonctionnelle avec tous les environnements de virtualisation standard supportant le format OVF. Mais,

seul VirtualBox a été testé et validé.

Attention : L’installation de la machine virtuelle doit être faite en dehors des périodes de

laboratoire encadrés

Installation pas à pas de la machine virtuelle

1. Installer VirtualBox en suivant la documentation officielle

URL de téléchargement: https://www.virtualbox.org/wiki/Downloads

Documentation : https://www.virtualbox.org/manual/ch02.html

Installer Virtualbox et l'extension pack. L'installation de l'extension pack se fait simplement en

double-cliquant sur le fichier .vbox-extpack téléchargeable à partir de la page Dowloads

donnée plus haut.

Si Virtualbox est installé sur un hôte Linux, ne pas oublier de rajouter l'utilisateur au groupe

vboxusers pour permettre l'accès aux périphériques USB depuis la machine virtuelle. Voir la

page de documentation (section 2.3.4 The vboxusers group) pour ce point.

Télécharger le fichier correspondant à la machine à l’adresse suivante

http://reds-data.heig-vd.ch/VMs/reds2017.ova

Il est préférable de se connecter au réseau de l’école via le réseau câblé plutôt qu’en wifi

pour ce gros téléchargement.

2. Démarrer VirtualBox Manager et choisir "Fichier > Importer une application virtuelle…" et

sélectionner le fichier téléchargé au point 2.

3. Valider l’importation de la machine virtuelle en cliquant sur Importer

⇒ La mise en place de la machine virtuelle démarre. Celle-ci peut durer plusieurs minutes

en fonction de la performance du PC hôte !

4. La machine virtuelle est créée et apparaît comme machine disponible dans VirtualBox

Manager.

ARO2 – Architecture des Ordinateurs 2 - Laboratoire Microarchitecture FETCH

- 3 -

5. Configurer le réseau de la manière suivante : Cliquer sur l’icône “Configuration”, puis, dans la

fenêtre qui vient de s’ouvrir, sélectionner accès par pont et votre carte réseau dans la liste.

6. Configurer un dossier partagé de la manière suivante : Cliquer sur l’icône “Configuration”

puis, dans la fenêtre qui s’est ouverte, sélectionner “Dossiers partagés”.

7. Cliquer sur l’icône avec un “+”, à droite, puis dans “Chemin du dossier”, sélectionner autre

et indiquer l’emplacement de votre dossier partagé hors VM. Donner un nom sous “Nom

du dossier” et cocher la case “Montage automatique”. Ce dossier sera trouvable dans la

colonne de gauche de l’explorateur de fichier dans la VM.

8. La VM peut maintenant être démarrée. Vous pouvez supprimer le fichier .ova du point 2.

ARO2 – Architecture des Ordinateurs 2 - Laboratoire Microarchitecture FETCH

- 4 -

Les utilisateurs de machines Apple (Mac OS) doivent reconfigurer la disposition du clavier dans la

machine virtuelle en allant dans le menu Applications > Settings Manager > Keyboard de la

machine virtuelle Linux et choisir le layout MacBook/MacBook Pro. La nouvelle disposition du clavier

ne prendra effet qu'au prochain login.

ARO2 – Architecture des Ordinateurs 2 - Laboratoire Microarchitecture FETCH

- 5 -

Déroulement du laboratoire

Pour ce laboratoire, vous devez télécharger les fichiers nécessaires avant de commencer votre

implantation.

Fichiers nécessaires

Vous devez télécharger à partir du site REDS un .zip contenant un template de répertoire

« workspace » contenant :

• Le fichier de travail Logisim template.circ avec deux horloges clk et sysclk

• Le fichier source du code assembleur main.S (le nom ne doit pas être modifié)

• Le fichier Makefile (ne doit pas être modifié) contenant les directives d’assemblage

Travail à effectuer

Créez un répertoire de travail ARO2_Ma_Fetch à partir du template « workspace » fourni. Ce

répertoire doit contenir les fichiers Logisim (.circ), main.S et Makefile.

Démarrez Logisim (menu->Education->Logisim). Effectuez la mise à jour si une fenêtre vous la

propose. Ouvrez le fichier .circ précédemment téléchargé.

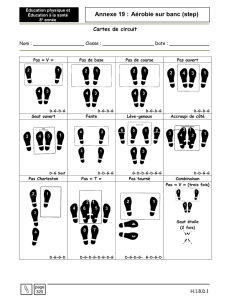

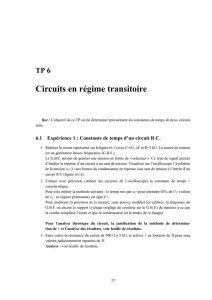

Etape 1 : Réaliser le circuit d’incrémentation du PC et de lecture du code d’instruction

• Prévoir un reset du registre PC avec un bouton.

• Placer des pins de sortie avec des noms significatifs (affichage hexa) sur le bus d’adresse et

la sortie de la mémoire.

• Utiliser une ROM pour la mémoire d’instruction, et non une RAM.

Attention : la ROM est adressée par mots de 16 bits, le bit 0 d’adresse du processeur ne doit pas

être câblé à la ROM (adresse divisée par 2).

Note : Vous devez utiliser uniquement l’horloge clk pour les circuits séquentiels. Attention de ne pas

supprimer l’horloge sysclk.

+

compteur de

programme

PC

DQ

mémoire

d'instruction

ADout

2

16 16

16

0xFB40

0xFB42

6

6

7

7

8

8

1

/

8

100%