Laboratoire 2 DECODE - REDS - HEIG-VD

Architecture des ordinateurs ARO2

Profs : C. Andrés Pena, R. Mosqueron

Assistants : Flavio Capitao, Anthony Convers, Alexandre Malki, Gaëtan Matthey

Laboratoire Microarchitecture DECODE

13/02/2017 – V1.7

-

1 -

Informations générales

Le laboratoire Microarchitecture dure 16 périodes et comprend 4 parties de 4 périodes chacune. Le

travail s’effectue par groupe de deux.

Le rapport à rendre portera sur deux labos (8 périodes au total) :

1) le laboratoire Microarchitecture FETCH (4 périodes).

2) le laboratoire Microarchitecture DECODE (4 périodes).

Le rendu s’effectue sous forme de dossier compressé contenant le workspace complet (projets

Logisim, codes assembleur), et le rapport (.pdf) envoyé à l’assistant de votre groupe.

• Code partie FETCH et partie DECODE avec rapport à rendre avant :

o ARO2-1-A : le 29.03.2017, 23h59 à flavio.capitaocantante@heig-vd.ch

o ARO2-1-B : le 30.03.2017, 23h59 à gaetan.matthey@heig-vd.ch

o ARO2-1-C : le 28.03.2017, 23h59 à anthony.convers@heig-vd.ch

o ARO2-1-D : le 28.03.2017, 23h59 à alexandre.malki@heig-vd.ch

N’oubliez pas de sauvegarder et d’archiver votre projet à chaque séance de laboratoire

Objectifs du laboratoire

L’objectif principal est la réalisation simplifiée de la partie DECODE d’un processeur en ajoutant une

banque de registres et en effectuant le traitement d’instructions de type Move. Vous recevrez un bloc

FETCH du processeur PRODIS et un programme à exécuter.

Ce laboratoire est noté. Vous devez rendre les projets Logisim, les codes assembleur et un rapport. Le

rapport doit montrer votre compréhension de l’architecture du bloc DECODE, de l’architecture d’une

banque de registre et de la technique de décodage des instructions.

Outils

Pour ce labo, vous devez utiliser les outils disponibles sur les machines de laboratoire (A07/A09) ou

votre ordinateur personnel avec la machine virtuelle fournie au premier labo.

ARO2 – Architecture des Ordinateurs 2 - Laboratoire Microarchitecture DECODE

- 2 -

Fichiers

Vous devez charger à partir du site REDS un .zip contenant un répertoire « workspace_labo2 » avec :

• Le fichier de travail Logisim Labo_decode_v2.circ (contenant le bloc FETCH de PRODIS)

• Le fichier source du code assembleur main.S (contenant un programme)

• Le fichier Makefile (ne doit pas être modifié) contenant les directives d’assemblage

Attention : Vous ne devez pas utiliser les fichiers du précédent laboratoire. Créez un nouveau

répertoire.

PRODIS, processeur didactique :

• Architecture ARM9 modifiée

• Bus adresses et bus données 16 bits

• 8 registres

• Quatre interruptions matérielles

• Pas de modes, pas d’exceptions

• Jeu d’instruction (réduit) 16 bits ARM Thumb

Donnée : 4 périodes en laboratoire + travail personnel

Créez un répertoire de travail ARO2_Ma_Decode à partir du répertoire « workspace_lab2 »

fourni. Ce répertoire doit contenir les fichiers Labo_decode_v2.circ, main.S et Makefile.

N’oubliez pas de relire votre cours ARO2 « Micro-architecture d’un processeur - La partie

DECODE » qui contient toutes les informations et exemples de circuit nécessaires pour réaliser

ce laboratoire.

Note : Respectez une architecture hiérarchique. Le bloc processeur doit être connecté à la mémoire

d’instruction et contenir les blocs Fetch et Decode (que vous allez réaliser). Vous pouvez placer la

banque de registre dans le bloc Decode ou au même niveau que les blocs Fetch et Decode dans le

bloc processeur.

Etape 1 : Un bloc FETCH est fourni (dans le bloc PRODIS).

Testez le bloc FETCH avec le programme assembleur fourni (vérifiez simplement que les instructions

sont lues successivement dans la mémoire).

Relevez un chronogramme des signaux qui vous paraissent importants dans le bloc FETCH.

ARO2 – Architecture des Ordinateurs 2 - Laboratoire Microarchitecture DECODE

- 3 -

Etape 2 : Créez une banque de 4 registres 16 bits (R0, R1, R2, R3) avec un bus de lecture (Read) et

un bus d’écriture (Write).

Testez le fonctionnement de votre banque (avant de la connecter au bloc FETCH) en écrivant et en

lisant des valeurs de registres. Mettez une copie d’écran de votre bloc en cours de test.

Astuce : pour tester le bloc, vous pouvez mettre des constantes sur les entrées, des probes sur les

sorties et générer une pulse WriteEn avec un bouton (utilisez la touche F2 pour activer la clock).

Outil : Vous pouvez visualiser en permanence le contenu de plusieurs registres dans l’onglet Register

(en bas à gauche) à condition de mettre « Yes » dans la propriété « Show in RegistersTab » des

registres dont vous voulez observer le contenu.

Etape 3 : Réalisez le circuit de décodage des instructions Move afin que le programme ci-dessous

(fourni dans main.S) fonctionne correctement.

MOV r0, #27

MOV r2, #4

MOV r3, #67

MOV r1, r3

MOV r0, r2

MOV r1, #0xAC

Relevez pour votre rapport un chronogramme de l’exécution de ces 6 instructions. Ce chronogramme

doit comporter les entrées et sorties de votre banque de registres et les valeurs des 4 registres durant

l’exécution.

Attention : Vous devez sauvegarder et rendre le fichier .circ de cette étape

**************************************************************

Tournez la page : Etape 4 sur la page suivante !!!!!!

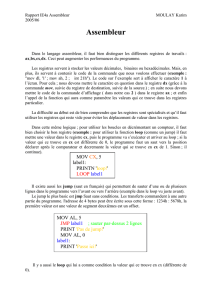

Banque

de

registres

Register_Read_Sel

Register_Read_Data

Register_Write_Sel

Register_Write_Data

Clock

Write

En

ARO2 – Architecture des Ordinateurs 2 - Laboratoire Microarchitecture DECODE

- 4 -

Etape 4 : Ajoutez un deuxième bus de lecture à votre banque de registre afin d’avoir deux registres

sources et un registre destination. Remplacez le programme précédent par celui-ci dans le fichier

main.S :

MOV r1, #2

MOV r3, #25

ADD r2, r1, r3

MOV r1, #12

ADD r0, r1, r2

MOV r3, r0

Modifiez votre circuit de décodage pour supporter l’instruction ADD. Vous devez utiliser le circuit

ADDER de Logisim pour l’addition.

Vérifiez que le programme ci-dessus fonctionne correctement. Relevez pour votre rapport un

chronogramme de l’exécution de ces 6 instructions.

Attention : Vous devez sauvegarder et rendre le fichier .circ de cette étape

1

/

4

100%