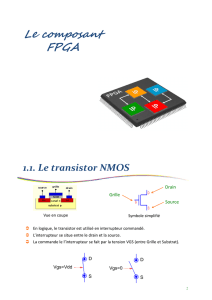

Les Circuits Reconfigurables : Passé, Présent, Futur ….

ªTechnologies microélectroniques en 2007 :

-Technologie de 90nm (voir 65nm)

- Intégration courante de plusieurs dizaines de millions de transistors… 1 milliard en 2004

- Fréquence de fonctionnement supérieures à 2GHz

0.18mm

256Mb DRAM

16 CPU FP 64b

500 MHz

0.07mm

4Gb DRAM

256 CPU FP 64b

2.5GHz

1999 2008

18 mm

30,000 pistes

1 clock

répéteurs tous les 3 mm

25 mm

120,000 pistes

16 clocks

répéteurs tous les 0.5 mm

Introduction & contexte

INTRODUCTION & CONTEXTE

Pourquoi les architectures reconfigurables ?

Les FPGA sont aujourd’hui de réelles alternatives aux ASIC

(capacité, prix et performances en adéquation avec les besoins)

Source : Altera, SOPC World Seminar S. Tredennick, The Rise of Reconfigurable Systems, ERSA 2003

Nombre de circuits

fabriqués

Source : L. Bossuet, G. Gogniat - LESTER

80% des design fonctionnent

àmoins de 200MHZ

Moyenne d’utilisation

Nombre de portes (log)

année

100M

10M

1M

100k

10k

1k

1989 2000 2007

CapacitémaxASIC

CapacitémaxFPGA

1000M

1997

1997

1999

1999

2001

2001

2003

2003

2005

2005

200 000 1 000 000

Coût de

fabrication

FPGA ASIC

2007

2007

1k

10k

100k

1M

10M

100M

1G

Less Complex More Complex

Algorithm Complexity

D

a

t

a

R

a

t

e

S

a

m

p

l

e

s

p

e

r

s

e

c

o

n

d

MPU/MCU

Single-Chip DSP

FPGA-Based

processing

ASIC

Multiple DSP Cores

or Chips

Pourquoi les architectures reconfigurables ?

1k

10k

100k

1M

10M

100M

1G

Less Complex More Complex

Algorithm Complexity

D

a

t

a

R

a

t

e

S

a

m

p

l

e

s

p

e

r

s

e

c

o

n

d

MPU/MCU

Single-Chip DSP

FPGA-Based

processing

ASIC

Multiple DSP Cores

or Chips

Pourquoi les architectures reconfigurables ?

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

1

/

21

100%