page de garde

MEMOIRE

En vue de l’obtention du diplôme de :

Magister en Electrotechnique

Option: Entrainements Electriques

Thème :

CONCEPTION D’UN CONTROLEUR D’ETAGE DE

PUISSANCE PAR FPGA

Présenté par : M

r

CHIBAH AREZKI

Soutenu le: Devant le jury composé de:

PRESIDENT :

M

r

. Chaibi Rachid : Professeur UMMTO

RAPPORTEUR:

M

r

. Laghrouche Mourad : Maître de conférences A UMMTO

EXAMINATEURS:

M

r

. Mohellebi Hacene : Professeur UMMTO

M

r

. Melah Rabah : Maître de conférences A UMMTO

REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE

MINISTERE DE L’ENSEIGNEMENT SUPERIEUR ET DE LA RECHERCHE SCIENTIFIQUE

UNIVERSITE MOULOUD MAMMERI DE TIZI OUZOU

Remerciements

A

AA

A

u terme de ce modeste travail, je tiens à exprimer mes vifs remerciements et

ma gratitude à :

M

r

Laghrouche M., maître de conférences au département d’Electronique, fa-

culté de Génie Electrique et d’Informatique à l’Université Mouloud Mammeri de Tizi

-Ouzou, pour m’avoir encadré et soutenu au cours de la réalisation de ce projet.

M

r

Auger F, maître de conférences hors classe, habilité à diriger des recherches au

sein de l’Ecole Polytechnique de Nantes Atlantique, pour son orientation, sa disponibilité,

son écoute, ses conseils et son soutien.

M

r

Chaibi R,

professeur au département d’Electrotechnique,

faculté de Génie

Electrique et d’Informatique à l’Université Mouloud Mammeri de Tizi-Ouzou, pour

m'avoir fait l'honneur d'accepter la présidence du jury de soutenance de ce mémoire.

M

r

Mohellebi H,

professeur au département d’Electrotechnique,

faculté de Génie

Electrique et d’Informatique à l’Université Mouloud Mammeri de Tizi-Ouzou, pour

m’avoir fait l’honneur d’examiner mon travail.

M

r

Melah R, maître de conférences

au département d’Automatique,

faculté de

Génie Electrique et d’Informatique à l’Université Mouloud Mammeri de Tizi-Ouzou,

pour m’avoir fait l’honneur d’évaluer ce travail.

J'

J'J'

J'

adresse mes sincères remerciements à M

me

Mansouri. O, pour ses encourage-

ments , son aide et son soutien qui m’ont été très précieux.

Que tous ceux qui ont contribué de près ou de loin à l’élaboration de ce travail;

trouvent ici ma profonde reconnaissance.

SOMMAIRE

Introduction Générale

Chapitre I- Apprentissage-approfondissement des circuits logiques

programmables, du langage VHDL et de la chaine de développement ISE-Weblink.

I-Introduction ……………………………………………………………………………...

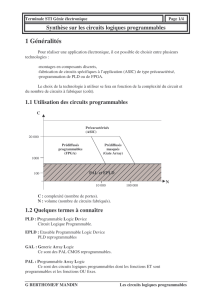

II-Circuits logiques programmables…………………………………….. .……………….

II-1- Introduction…………………………………….. …………………………………..

II-2 Définition des PLDs………………………….. .…………………………………….

II-3- Structure de base d’un PLD………………………………………………………….

II-4- Les différentes familles de PLD…………………………………………………….

II-4-1- Les PALs…………………………………………………………………………..

II-4-2- Les GALs………………………………………………………………………….

II-4-3- Les EPLDs (Erasable Programmable Logic Device)………………………………

II-4-4- Les CPLDs ( Complex programmable logic device)………………………………

II-4-5- Les FPGAs (Field Programmable Gate Array)…………………………………….

II-5- Les FPGAs …………………………………………………………………………..

II-5-1- Présentation………………………………………………………………………...

II-5-2- Classification des FPGAs………………………………………………………….

II-5-2-1- FPGAs à SRAM…………………………………………………………………

II-5-2-2- FPGAs à Anti-fusible…………………………………………………………….

II-5-3- Familles des FPGAs de XILINX………………………………………………….

II-5-3-1- Famille SPARTAN 3E…………………………………………………………...

II-5-3-2- Architecture interne d’un circuit SPARTAN 3E ……………………………….

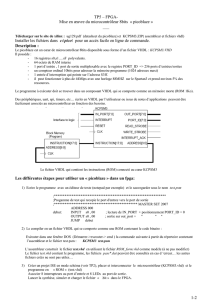

III- Chaine de développement……………………………………………………………..

IV - Langage de description VHDL…………………………………………….

IV -1-Introduction…………………………………………………………………………

IV -2- Définition du VHDL……………………………………………………………….

IV -3- Structure d’une description VHDL…………………………………………………

IV-3-1- Entité………………………………………………………………………………

IV 3-2- Architecture……………………………………………………………………….

IV-3-2-1-Description comportementale…………………………………………………...

IV-3-2-2-Description structurelle………………………………………………………….

IV-3-2-3-Description Mixte………………………………………………………………..

1

4

4

4

4

5

6

6

7

8

9

9

10

10

13

13

14

14

15

15

19

20

20

21

21

21

22

22

23

24

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

61

61

62

62

63

63

64

64

65

65

66

66

67

67

68

68

69

69

70

70

71

71

72

72

73

73

74

74

75

75

76

76

77

77

78

78

79

79

80

80

81

81

82

82

83

83

84

84

85

85

86

86

87

87

88

88

89

89

90

90

91

91

92

92

93

93

94

94

95

95

96

96

97

97

98

98

99

99

100

100

101

101

102

102

103

103

104

104

105

105

106

106

107

107

108

108

109

109

110

110

111

111

112

112

113

113

114

114

115

115

116

116

117

117

118

118

119

119

120

120

121

121

122

122

123

123

124

124

125

125

126

126

127

127

128

128

129

129

1

/

129

100%