Les circuits logiques programmables

Terminale STI Génie électronique Page 1/4

Synthèse sur les circuits logiques programmables

G BERTHOME/F MANDIN Les circuits logiques programmables

1 Généralités

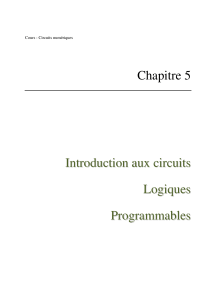

Pour réaliser une application électronique, il est possible de choisir entre plusieurs

technologies :

-montages en composants discrets,

-fabrication de circuits spécifiques à l’application (ASIC) de type précaractérisé,

-programmation de PLD ou de FPGA.

Le choix de la technologie à utiliser se fera en fonction de la complexité du circuit et

du nombre de circuits à fabriquer (coût).

1.1 Utilisation des circuits programmables

C : complexité (nombre de portes).

N : volume (nombre de circuits fabriqués).

1.2 Quelques termes à connaître

PLD : Programmable Logic Device

Circuit Logique Programmable.

EPLD : Erasable Programmable Logic Device

PLD reprogrammables

GAL : Generic Array Logic

Ce sont des PAL CMOS reprogrammables.

PAL : Programmable Array Logic

Ce sont des circuits logiques programmables dont les fonctions ET sont

programmables et les fonctions OU fixes.

N

C

10 000 100 000

100

1000

20 000

Précaractérisés

(ASIC)

Prédiffusés

programmables

(FPGA)

Prédiffusés

masqués

(Gate Array)

PAL et EPLD

Terminale STI Génie électronique Page 2/4

Synthèse sur les circuits logiques programmables

G BERTHOME/F MANDIN Les circuits logiques programmables

2 Les GAL

2.1 Les différents types de sorties

2.1.1 Sortie de type C (Combinatoire)

Ces sorties 3 états sont rebouclées vers la matrice de fusibles. Une sortie peut donc

servir de variable intermédiaire. En mode haute impédance (la sortie étant inhibée), on peut

utiliser une broche de sortie comme étant une entrée. On parle alors d’entrée/sortie (I/O).

2.1.2 Sortie de type R (à Registre)

Ces sorties utilisent une bascule D qui permet la logique séquentielle. Par contre, une

sortie à registre ne peut pas être utilisée comme entrée.

2.1.3 Sortie de type V (Versatile)

Le bloc de sortie des GAL versatiles permet de configurer (par programmation) le

mode d’utilisation de la broche de sortie :

Terminale STI Génie électronique Page 3/4

Synthèse sur les circuits logiques programmables

G BERTHOME/F MANDIN Les circuits logiques programmables

2.2 La programmation JEDEC

L’opération de programmation se fait par un programmateur de laboratoire qui obéit à

un fichier transmis au standard JEDEC.

Ce fichier est produit par un outil de développement (PROTEUS, ISP Design

Expert(Lattice), …), qui permet de saisir les équations de programmation du GAL et d’en

simuler le fonctionnement.

La tension qui sert à programmer les GAL est 12V.

Dans certains GAL, il est possible de les interdire de relecture en faisant fondre un

fusible appelé « security fuse » ou « security bit ».

2.3 Désignation du GAL

GAL (CE) 16 R 8 H 15 PC

Type de boîtier

Vitesse (Temps de Propagation en ns

Consommation (demi-puissance)

Sorties (8)

Registre (structure de sortie)

Nombre d’entrées (16)

Facultatif, chez AMD indique CMOS

GAL

Terminale STI Génie électronique Page 4/4

Synthèse sur les circuits logiques programmables

G BERTHOME/F MANDIN Les circuits logiques programmables

3 Exemple de programme permettant de produire le

fichier JEDEC : le langage ABEL

Il existe plusieurs langages qui permettent de produire le fichier JEDEC un de

ceux-ci est le langage ABEL dont voici un exemple.

MODULE exemple

TITLE 'exemple de simulation'

Declarations

Clk pin 1 ;

Q1 pin 16 ;

Equations

Q1 = E1&E3#E2 ;

Q2 = !Q1 ;

Q3 = !E3 ;

END exemple;

La directive module et le nom

du fichier constitue la

première ligne.

La directive title permet de

proposer les informations (titre,

date, nom du concepteur, etc…)

Le mot clé declarations permet :

-affecter les noms des entrées/sorties

aux numéros des broches du composant,

-les broches non utilisées ne sont pas

déclarées,

-la directive est pin

Le mot clé equations permet :

-spécifier l’évolution des sorties en

fonction des entrées.

Le symbole = est l’affectation.

La directive end suivie du nom du module

marque la fin du programme source.

1

/

4

100%