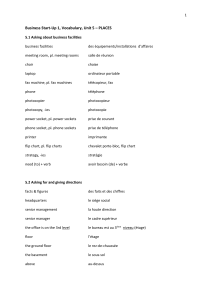

Introduction aux Systèmes Numériques - CEA-Irfu

FPGA - Cellule de Base

herve.le-prov[email protected]

2

i(n..1) Look Up Table

(LUT) M

U

X

FLIP

FLOP o

clock reset

Cellule de Base (CB)

Configuration statique

(SRAM)

FPGA : Field Programmable Gate Array

FPGA - Lego

herve.le-prov[email protected]

3

CB

MR

CB

MR

CB

MR

CB

MR

IBUF

i0

OBUF o

IBUF

i1

Matrice de Routage

Cellule de Base

Ligne de routage Verticale

Ligne de routage Horizontale

Buffer d’entrée

Buffer de Sortie

FPGA - Lego

herve.le-prov[email protected]

4

CB

MR

CB

MR

CB

MR

CB

MR

IBUF

i1

OBUF o

IBUF

i2

o <= i1 and i2;

FPGA-Logique Asynchrone

herve.le-prov[email protected]

5

i1

i2

o

o

i1

i2

FPGA

Glitch

FPGA

SYSTEME CONVERTISSEUR

NUMERIQUE/

ANALOGIQUE

MEMOIRE

o

CPU

Analyse au niveau système

des conséquences d’un

glitch :

•Ordre de conversion N/A

erroné

•Ecriture mémoire erronée

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

1

/

25

100%