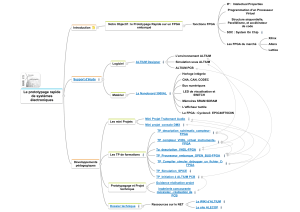

Les circuits FPGA Field Programmable Gate Array

Implantation de processeurs dans les FPGA et ASIC

Processeur « softcore »

(SoPC : System on Programmable Chip)

Quelques processeurs « softcore »

•Propriétaires:

–Picoblaze(8bits) Microblaze (Xilinx)

–NIOS (Altera)

–Arm CortexM1 (Arm) implantable sur FPGA Actel, Altera et Xilinx

•Open Source:

–Micro8 Micro32 (Lattice)

–LEON (Gaisler Research)

–OpenRISC (opencores.org)

•Autres:

–Z80, 8051, 6502, 68xx…

Bibliographie

• Datasheets et notes d’applications des fabricants de

FPGA et des concepteurs de systèmes sur silicium

–www.actel.com

–www.xilinx.com

–www.altera.com

–www.lattice.com.

–www.arm.com

–www.opencore.org

etc…

Conception du circuit

et

Conception du programme

Conception du circuit

•Langage HDL, schéma ou interface graphique spécifique

•Choix des périphériques (UART, Timers, ADC..)

–Bloc IP dans le FPGA (softcore)

–Circuits externes à connecter au FPGA (matériel)

–Compatibilité des signaux et des vitesses des bus

•Câblage du processeur et des périphériques

–Choix du plan mémoire

–Interfaçage des bus si les périphériques ne sont pas compatibles avec le

processeur.

Conception du programme

•Développé en général avec des outils traditionnels

(assembleur,compilateur, linkeur…)

–Le plan mémoire doit être pris en compte

–Importance du fichier de linkage

•Implantation du programme

–Dans le FPGA

» Bloc HDL simulant une ROM et son contenu à connecter

» Fichier binaire dans un bloc de mémoire FLAH interne

» Transfert éventuel et exécution en RAM interne

– À l’extérieur du FPGA

» mémoire FLASH externe connectée au FPGA

» Transfert éventuel en RAM pour le débogage ou exécution plus

rapide

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

1

/

33

100%