T.P 4: Unité logique

T.P 4: Unité logique

1. Préparation théorique:

1.1. Rappeler l'équation du OU EXCLUSIF:

S = f(E,K) =

puis indiquer l'équation dans les cas suivants:

E K = 0 => S=f(E,0) =

=1 S

K K = 1 => S=f(E,1) =

K permet donc d'obtenir une fonction OUI ou une fonction NON pour S.

1.2. Table de vérité réduite, pour laquelle il n'y a qu'une entrée: K.

Dans la colonne de la sortie S apparait la variable E. Donner cette table.

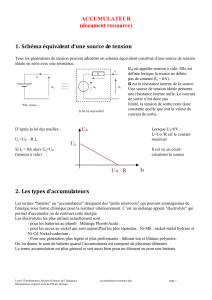

1.3. Utilisation du OUEX pour réaliser une unité logique rudimentaire:

A

=1 A'

z0

& S'

B =1 S

=1 B'

z1 z2

A’= A OUEX z0 B’=B OUEX z1

S’=A’.B’ S = S’ OUEX z2

Conformément à l'étude faite lors de la question 1, on peut obtenir selon les valeurs

respectives de z0, z1 et z2, les valeurs:

A ou /A pour A' (selon la valeur de z0) et

B ou /B pour B' (selon z1) et enfin

S' ou /S' pour S (selon z2).

on a toujours S' = A' . B'

par exemple pour z0= 0, z1=1 et z2=0, on obtient:

z0=0 => A'=A

z1=1 => B'=/B

z2=0 => S=S' donc S=A./B

écrire, en appliquant le même raisonnement, les équations de S’ et S en fonction de A et

B pour chacune des combinaisons de z0, z1 et z2:

Z0

Z1

Z2

S'

S

0

0

0

0

0

1

0

1

0

A./B

A./B

0

1

1

1

0

0

1

0

1

1

1

0

1

1

1

Compléter le tableau en donnant les équations de S’ et S en fonction de A et B.

2. Câblage:

Câbler le circuit du paragraphe précédent : utiliser un boîtier OUEX (86) et un boîtier ET

(08) .

Utiliser des interrupteurs pour Z0, Z1, Z2, A et B.

Vérifier que pour :

Z0=0 z1=0 z2=0 on obtient S=A.B

Z0=0 z1= 0 z2=1 « « S=/(A.B)

Z0=1 z1=1 z2=1 « « S=A+B

Z0=1 z1=1 z2=0 « « S=/(A+B)

3. Essai du PAL « UL »:

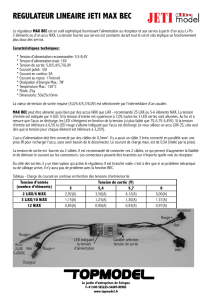

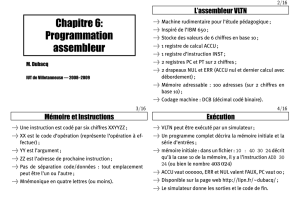

Présentation du circuit PAL 20V10

circuit avant programmation, indiquant les fonctions possibles des différentes

broches.

Un PAL est un circuit intégré programmable : il contient des réseaux de ET et de OU dont

les interconnexions internes sont effectuées par un appareil appelé programmateur

qui génère les connexions indiquées dans un fichier. Ce composant est reprogrammable.

Le PAL avec l’étiquette « UL » contient un programme dont le schéma équivalent est celui

du circuit étudié dans la question précédente.

Les broches utilisées sont les suivantes :

A broche 2, B broche 3, z0 broche 4, z1 broche 5, z2 broche 6, S broche 23

Câbler et tester le fonctionnement (fonctions OU, ET, NON OU, NON ET).

IN / OUT / Q

IN / OUT / Q

IN / OUT / Q

IN / OUT / Q

IN / OUT / Q

IN / OUT / Q

IN / OUT / Q

IN / OUT / Q

IN / OUT / Q

IN / OUT / Q

IN /CLK

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

GND

Vcc

IN

1

12

24

4. Décodeur d'instructions:

Le circuit précédent peut être considéré comme l'embryon d'une Unité Logique puisque

selon le code de commande placé sur z0, z1 et z2 on peut obtenir 8 équations logiques

(on ne peut cependant pas obtenir S= A, S= B, S=/A , S=/B ainsi que les

OUEXCLUSIFS).

Le système peut être également représenté ainsi:

z2

z1

z0

A

UL

S

B

z0, z1 et z2 permettent de choisir la fonction réalisée par le système, on dit aussi

l’INSTRUCTION.

A et B sont les entrées de données du système.

S est donc le résultat de l’instruction codée sur z2, z1 et z0, sur les données A et B.

On désire utiliser seulement les 4 instructions: OU, NON OU, ET et NON ET.

Le choix entre ces 4 instructions est donc possible avec seulement deux signaux (ZD0 et

ZD1)

Le système complet devient:

ZD0 z2

décodeur z1

ZD1 z0

A

UL

S

B

ZD0 et ZD1 sont les bits qui contiennent le code de l’instruction. On a choisi d’utiliser

les codes suivants pour ZD1 et ZD0:

ZD1 ZD0 z0 z1 z2

0 0 A OU B

0 1 NON (A ET B)

1 0 NON (A OU B)

1 1 A ET B

Compléter la table de vérité en plaçant les valeurs de z0, z1 et z2 pour obtenir les

instructions, conformément aux études précédentes.

Concevoir le décodeur : équations de z0, z1 et z2 en fonction de ZD1 et ZD0; schéma ;

câblage et test en utilisant le circuit PAL « UL ».

Définition : on appelle BUS un ensemble de signaux logiques qui sont porteurs,

ensemble, d’une information.

Afin de ne pas alourdir les schémas un bus est représenté par une seule ligne avec un

petit tiret oblique pour indiquer que cette connexion comporte plusieurs fils, on indique le

nombre de fils (bits) à coté :

Cette représentation est celle d’un bus de 32 bits, 32 liaisons (fils, bits) porteurs d’une

information.

Pour notre processeur rudimentaire le bus de données transmet en parallèle un certain

nombre de bits :

Des bits indiquant l’opération à effectuer (code instruction)

Des bits indiquant la donnée à traiter par l’opération

(pour concevoir notre système complet il faudrait ajouter une mémoire dans laquelle se

trouve les codes successifs composant notre programme . Il faut alors ajouter un circuit

mémoire)

1. Unité de calcul:

Une unité de calcul (généralisation d'une unité logique, obtenue en ajoutant des

possibilités de calcul arithmétique, de décalages…) peut être représentée de la façon

suivante:

2. Accumulateur

Puisque le système doit transmettre le code de l’instruction et un opérande en même

temps cela oblige, pour les opérations à 2 opérandes, d’avoir mémorisé un des

opérandes.

Par exemple pour réaliser l’opération 010 ET 011 (c’est-à-dire faire un ET entre les

valeurs 2 et 3 en binaire) il faut:

Charger 2 :

010, premier opérande

code de chargement (mémorisation =>R=X)

Additionner 3

011 second opérande

code du ET (R=X ET Y)

3

X

R

3

Y

Unité de

calcul

32

2

3

(Stocker résultat)

Le premier opérande est mémorisé dans des bascules D : le registre accumulateur .

La mémoire nécessaire, appelée aussi registre interne, accumulateur, est reliée de la

façon suivante :

Sur le bus de données parviennent en même temps le code de l’instruction (C) et

l’opérande (X).

Les opérations sont faites entre X, donnée transmise avec le code de l’opération sur le

bus de données, et Y, valeur précédemment mémorisée dans l’accumulateur (par une

instruction de chargement, ou résultat d’une opération précédente).

Pour chaque instruction il y a deux temps :

Présentation du code et de l’opérande : le résultat est immédiatement obtenu en

R

Front sur clock pour mémoriser le résultat dans l’ACCU

Travail demandé:

On utilise un PAL, repéré par l’étiquette UL2, et un circuit 74LS175 dont voici les

brochages:

xx175 PAL2

Unité de

calcul

X

Y = ACCU

R

C

Registre

accumulateur

clock

ACCU

BUS DE

DONNEES

BUS DE

DONNEES

33

3

2

R0

R1

R2

X0

X1

X2

Y0

Y1

C1

C0

Y2

GND

Vcc

1

12

24

6

6

7

7

1

/

7

100%