Weitere Files findest du auf www.semestra.ch/files DIE FILES

Microprocesseur I02

- 1 -

Classification des microprocesseurs

orienté accumulateur

orienté registres généraux

pile (stack)

• Le jeu d’instructions est lié

aux accumulateurs, par ex.

-

charge la valeur A5 dans

l’accu "a"

• µP : 68HC11

• Le jeu d’instructions est

déclinable avec un registre

(la commande est indépendant

du registre), par ex.

-

• µP : Indel

Microprocesseur 68HC11

Exemple du CCR: (condition code register)

LDAA # val

bit no. 7 = 1 négatif

S

X

H

I

N

Z

V

C

-

-

-

-

0

-

- flag non modifié

0 flag mit à 0

1 flag mit à 1

flag prend la valeur

correspondante de la

de la commande.

Classification des instructions 68HC11

Registre mémoire : ldaa, ldx

Registre registre :

Arithmétique : aba, adda

Logic : and, or, eor

Shift & rotate : asl, asr, lsa, lsr, lsl, rol, ror

-128 | 127

-1 0 1

N=1

Z=0

V=0

N=0

Z=0

V=0

N=0

Z=1

V=0

Microprocesseur I02

- 2 -

Différance shift & rotate:

Shift:

avant:

0

0

0

1

1

0

0

1

après:

0

0

1

1

0

0

1

0

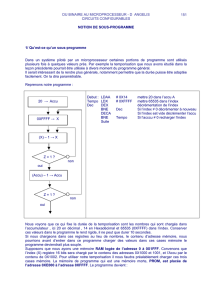

Jump: bra, beq, bnc, …

Subroutines: bsr, gsr, …

Interruption: cli

Instruction est composé d’un opcode + un ou plusieurs opérande(s)

Mode d’adressage:

Le mode d’adressage est la manière dans la quelle le microprocesseur « appelle » une case mémoire.

La commande utilisée détermine le mode d’adressage. Certaine commandes peuvent être utilisé en

différents modes.

Le 68HC11 a 8 modes d’adressages:

1) inhérent (implicite)

• uniquement l’opcode (il n’y a pas de opérande(s))

• l’élément adressé est inclus dans l’opcode

ex. : ABA add accu B à accu A accu A

CLRA clear A ( LDAA #0)

MUL accu A * accu B accu D

2) immédiat

• transfert l’opérande dans le registre mentionné par

l’opérande

ex : LDAA #$07 charge la constante 07 accu A

3) directe (8 bit)/ étendu (16 bit)

• opérande spécifie l’adresse d’une case mémoire

(l’élément adressé)

ex : LDAA $0FFF

$86

$07

$07

opcode

opérande

accu

$A5

$A5

$0FFF

accu

Microprocesseur I02

- 3 -

4) indexé

• l’élément adressé (la case mémoire) est pointé pas les

registres d’index X et Y.

ex :

• adresse de l’élément = valeur de registre d’index +

offset

LDX #bidon bidon est défini à #1000

LDAA 0,X

est égal à LDAA bidon

5) relatif

• modification (une addition/soustraction du PC)

• valeur additionné / soustraite exprimé par 1 byte

[-127…+128]

ex : branch conditionnel, loop

• le déplacement est calculé par l’assembleur

# : adressage immédiat

$ : chiffre en format hexadécimal

PC : program counter

Bloc diagramme du 68HC11

Page 239

Arithmetic Logical Unit (ALU)

- operatinos arithmétiques (add, mul, …)

- opératinos logiques (And, Or, Not, Shift, …)

Instruciton Register (IR)

- contient l’opcode de l’instruction

Exemple :

LDAA 0,Y

registre d‘index utilisé

offset (+/-) exprimé sur 1 byte [-128…+127]

$A4

$A5

$A6

$A5

$1000

accu

Microprocesseur I02

- 4 -

Load value $2000 into register X :

LDX #$2000

Store value from accu A into RAM at

address $2000 :

STAA $2000

X=$6000

PC=$2000

Address mode: indexed

1) fetch: get instruction

2) decode: get operand

3) execute: calculate address

4) fetch value from RAM to

put it into accu A

6

6

1

/

6

100%