1.2.3 Exécution des instructions du microprocesseur fictif

LE

MICROPROCESSEUR

1

Sommaire

Partie 1 : L’unité centrale du microprocesseur

Partie 2 : La mémoire centrale du microprocesseur

Partie 3 : Les périphériques et interfaces associées au microprocesseur

Partie 4 : Logiciel

1 L’UNITE CENTRALE DU MICROPROCESSEUR

Plan

Introduction

Etude d’un cas d’école

Principes généraux de conception d’une unité centrale

Quelques exemples

Etude d’un composant du marché

Notions de programmation en langage d’assemblage

1.1 INTRODUCTION

Le but de ce chapitre est de mettre en évidence les principaux constituants d’une unité centrale. Dans les

chapitres précédents, on a mis en évidence la structure d’une :

ALU ou UAL (Unité arithmétique et logique) permettant de réaliser différentes opérations grâce à un

décodeur

MEMOIRE et en particulier les lignes RD/WR associées ; CS, les bus d’adresse et de données. Ce type

de circuit permet de stocker de l’information pour un usage futur.

1.1.1 Instructions évoluées

Voyons maintenant les instructions évoluées, dites instructions machine (pour assembleurs). Soit l’instruction

suivante (en pseudo-langage) :

Avant la phrase d’exécution, chaque identificateur A, B, C est représenté par une zone de mémoire d’adresse

connue notée &A, &B, &C (arbitrairement et symboliquement).

Remarque : on notera également [X] la valeur du mot d’adresse symbolique X.

Pour coder l’instruction {1}, on doit utiliser trois instructions différentes utilisant l’accumulateur (zone mémoire

interne à l’UC).

Pour le codage de l’instruction {1} :

Load &A ; ACCU[&A]

Add&A; ACCU[ACCU]+[&B]

Store&C; &C[ACCU]

Pour le codage de l’instruction {2} :

Load &C ; ACCU[&C]

Comp 0; [ACCU]::0

Jg 43; Aller à l’adresse 43 si [ACCU]>0, sinon on va à l’instruction

C :=A+B {1}

If C>0 then action_1 {2}

action_2

2

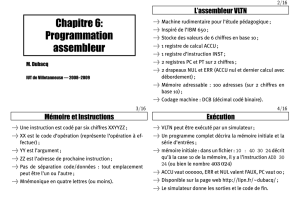

1.2 ETUDE D’UN CAS D’ECOLE

1.2.1 Etude d’un microprocesseur fictif

Principales caractéristiques :

Mot de 8 bits par instruction et données

Adresse sur 6 bits, donc 64 mots adressables

Un registre ACCU de 8 bits

Un jeu de 4 instructions de format général :

Le jeu d’instruction est le suivant :

Load M (code : 00) ACCUM

Store M (code : 01) M[ACCU]

Add M (code : 10) ACCU[ACCU]+[M]

Sub (code : 11) ACCU [ACCU]-[M]

1.2.2 Exécution d’un programme du microprocesseur fictif

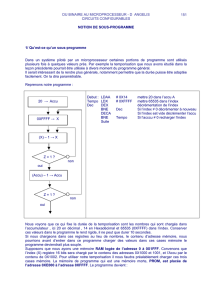

Schéma du processeur fictif. Ce schéma est a connaître parfaitement.

Exercice :

Faire tourner ce processeur avec les données en mémoire.

1.2.3 Exécution des instructions du microprocesseur fictif

Deux remarques avant d’examiner en détail le schéma global du processeur.

Le cycle d’exécution d’une instruction se divise en deux phases :

Code

opération

2 bits

Adresse 6

bits

MEMOIRE

3D

BE

7F

…

0B

0D

4F

Buffer d’ES

Buffer d’adresse

UAL

(+, -)

ACCU

PC (00 au début)

Registre

d’instructions

Décodeur

d’instruction et

unité de contrôle

Signaux de contrôle

(UAL et portes)

données

adresses

3

Fetch ou recherche d’instruction (et chargement dans le registre d’instruction)

Exécution proprement dite

Pour l’écriture, l’adresse est dans le buffer d’adresse, les données sont dans le buffer ES et il faut valider la

bascule d’écriture.

Pour la lecture, l’adresse est dans le buffer d’adresses, il faut valider la bascule de lecture et le résultat se trouve

dans le buffer ES.

Note : Un buffer est un registre lié à un bus (voir schéma global du processeur).

1.3 PRINCIPE GENERAUX DE CONCEPTION D’UNE UNITE CENTRALE

CLASSIQUE

1.3.1 Classification générale des instructions

On distingue 4 classes :

Mouvement de données entre registres et mémoire centrale.

Instructions arithmétiques et logiques : +, *, /, -, in(dé)crémentation, et, ou, comparaisons, décalage,

rotation, complémentation.

Instructions de contrôles ou branchements conditionnels, inconditionnels.

Instructions de gestion de l’environnement, mise à jour, opérations d’ES, positionnement, lecture des

masques de bits, interruptions et indicateurs.

1.3.2 Les opérandes

En plus du code opération, c’est ce dont à besoin l’unité centrale pour pouvoir exécuter l’instruction. Par

exemple, pour effectuer une addition, on a besoin de deux opérandes au moins (opérateurs binaires) et il faut

aussi prévoir ou mettre le résultat.

Le nombre des opérandes peut être variable :

Htl (halt) est une instruction sans opérande

Jmp adr est une instruction à un opérande (adr)

Mov reg1 reg2 est une instruction à deux opérandes (reg1 et reg2)

1.3.3 Modes d’adressages de base

Il existe différents types d’adressage. Exemples avec lda :

Lda M : accu[M] : adressage direct

Lda #n : accun : adressage immédiat

Lda[M] : accu contenu de l’adresse contenue à l’adresse M

Lda[M][SI] : accu contenu (de l’adresse contenue à l’adresse M + compteur SI)

1.3.4 Réalisation d’une instruction

Le concepteur d’une unité centrale à deux possibilité pour implémenter les instructions interprétée par l’unité

centrale :

Câblage : on câble directement l’instruction (par un circuit). La technologie est alors dite « adaptée ».

Cela a l’avantage d’être rapide à l’exécution mais cela peut être complexe, donc cher.

Microprogrammation : une instruction est considérée comme une fonction ou une procédure constituée

de micro-instructions câblées. L’instruction est enregistrée en mémoire morte. Avantage : le circuit du

microprocesseur est plus simple et le jeu d’instruction est modifiable, mais la vitesse d’exécution est

assez peu élevée.

Lorsque le jeu d’instruction est limité, on peut procéder de la manière suivante :

Emulation : ou simulation logicielle (instruction=fonction assembleur ou langage C) ; inconvénient :

lent !

Ajout d’un co-processeur câblé ou mono-programmé (processeur spécialisé qui exécute des instructions

spécifiques) ; l’unité centrale sous traite. Par exemple, le co-processeur arithmétique 80xx7 associé au

80xx6 réalise les opérations en virgule flottante et les fonctions mathématiques.

4

Architecture pipeline du microprocesseur 8088 d’intel.

Deux unités :

- EU : Execution Unit : utilise les fonctions logiques et arithmétiques

- BIU : Bus Interface Unit : stocke par anticipation 6 octets de codes dans une file.

Cas d’un vrai microprocesseur standard :

fetch

exec

fetch

Exec…

Cas de l’architecture pipeline

Pendant que l’EU exécute une instruction, le BIU va chercher en mémoire la prochaine instruction et la

stocke dans sa file :

fetch

fetch

fetch

fetch

fetch

attente

Exec1

Exec2

Exec3

Exec4

La durée de traitement est donc bien plus courte mais en cas de rupture de séquence (jump, branchement) le

contenu de la file doit être réinitialisé.

1

/

5

100%