Rappels de cours

AMSI 2001/2002 Joëlle Delacroix

1

EXERCICES DIRIGES 5, 6 et 7

MODES D'ADRESSAGES

EXECUTION DES INSTRUCTIONS MACHINES

Rappels de cours

A. Notion d'instructions, modes d'adressages

Le langage de programmation d'une machine est un ensemble d'instructions permettant de

spécifier à la machines les opérations à exécuter pour résoudre un problème donné. Il existe

différents niveaux de langages.

Au niveau de la machine physique se trouve le langage dit langage machine, seul exécutable par

la machine. Les instructions du langage machine sont des mots binaires.

Le schéma ci-dessous résume les différents niveaux de langages existants sur une machine :

- le langage de haut niveau (C, ada, Cobol, etc…) est indépendant de la machine

physique et ne peut pas être directement exécuté par celle-ci.

- le langage d'assemblage est dépendant de la machine. Il est équivalent au langage

machine à la différence près que les chaines binaires de l'instruction machine sont

remplacées par des chaines mnémoniques.

- le langage machine est composé des instructions directement exécutées par le

processeur.

Langage haut niveau

COMPILATEUR

Langage assemblage

ASSEMBLEUR

Langage machine

Indépendant

matériel

Dépendant

matériel

I := 1;

J := 3;

I = J + I;

LOAD Im R0 1

LOAD Im R1 3

ADD Rg2 R0 R1

00000000000011110000000000000001

00000000000010100000000000000011

0010111100000001

AMSI 2001/2002 Joëlle Delacroix

2

On se réfère à la documentation MAP32 pour étudier le format des instructions et les différents

types d'instructions.

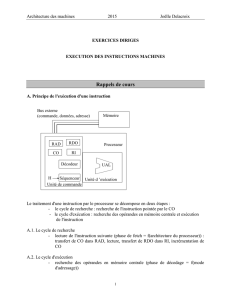

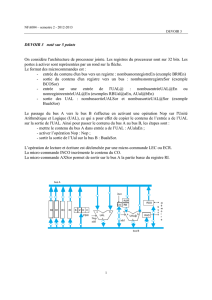

B. Principe de l'exécution d'une instruction

Unité de commande

Unité d ’exécution

Mémoire

Processeur

CO RI

Décodeur

Séquenceur

H

UAL

RAD RDO

Bus externe

(commande, données, adresse)

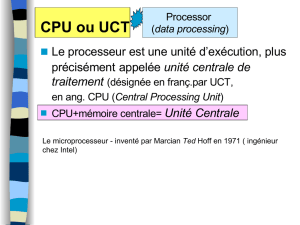

Le traitement d'une instruction par le processeur se décompose en deux étapes :

- le cycle de recherche : recherche de l'instruction pointée par le CO

- le cycle d'exécution : recherche des opérandes en mémoire centrale et exécution

de l'instruction

A.1. Le cycle de recherche

- lecture de l'instruction suivante (phase de fetch = f(architecture du processeur)) :

transfert de CO dans RAD, lecture, transfert de RDO dans RI, incrémentation de

CO

A.2. Le cycle d'exécution

- recherche des opérandes en mémoire centrale (phase de décodage = f(mode

d'adressage))

- exécution de l'instruction (phase d'exécution = f(code opération)

Les circuits de commande et de séquencement sont pilotés par une horloge à quartz. Le quartz est

externe au processeur; en revanche, les circuits d'horloge peuvent être internes ou externes au

processeur.

AMSI 2001/2002 Joëlle Delacroix

3

UAL Registres

Décodeur

Horloge

Séquenceur

Quartz

UAL Registres

Décodeur

Horloge

Séquenceur

Quartz

Une horloge à 50 Mhz fournit une période d'horloge ou microcycle ou cycle machine de

1/50000000 = 20 ns. Les cycles de recherche et d'exécution forment le cycle d'instruction. Ce

cycle d'instruction s'étend sur plusieurs cycles machine.

1234567 891011

Cycle instruction

Cycle recherche Cycle

exécution Cycle recherche

H

C. Les micro commandes

Pour permettre le transfert des données entre les différentes entités connectées sur les bus du

processeur, des barrières en entrée et en sortie doivent être implantées. Ces barrières sont

symbolisées par un rond sur les connexions aux bus sur les schémas des processeurs qui suivent.

Exemple sur le premier schéma de processeur : registre R1 connecté aux Bus A et B. Les

barrières en entrée et en sortie du registre R1 sont contrôlées par les barrières nombusR1En et

nombusR1Sor. Quand nombusR1En est activée, la donnée disponible sur le bus nombus est

chargée dans R1. Quand nombusR1Sor est activée, la donnée disponible dans R1 est placée sur le

AMSI 2001/2002 Joëlle Delacroix

4

bus nombus. Quand nombusR1Sor est désactivée, le bus peut être utilisé pour véhiculer des

données à partir d'autres registres.

Exemple :

Transférer le contenu de R1 dans le registre R4

AR1Sor, CAB (liaison entre bus qui quand elle est activée, permet le transfert de données du bus

A vers le bus B) BR4En

On ne donne ici que les microcommandes activées, les autres étant par défaut non activées.

L'ensemble des microcommandes activées sur un cycle horloge forme une microinstruction.

L'ensemble des microinstructions constitue le microprogramme exécuté par l'unité de commande.

On compte pour les microcommandes

- les activations de porte

- les signaux de commandes liés au bus externe (LEC, ECR notamment)

- les commandes de sélection (S) sur les UALs

Exercices

Exercice 1. Manipulation des modes d’adressages

A l'issue de l'exécution du code assembleur suivant et compte tenu de l'état initial de la mémoire

et des registres du processeur, la case mémoire d'adresse (1000)16 a pour contenu la valeur

10016 ? 'a'? 199810 ?

Adresse (base16) Contenu Registre Contenu

1000 a Rsp 500

1001 b RIX 100

1002 2000

1003 d

2000 3000

2010 305

LOAD D R0 (1002)16

LOAD Im R1 (1002)10

PUSH D (1000)10

ADD Rg2 R0 R1

NEG Rg1 R1

ADD I R1 (1002)16

STORE Ix R1 (900) 16

AMSI 2001/2002 Joëlle Delacroix

5

Exercice 2. Code Assembleur

Expliquez ce que fait le programme assembleur qui vous est donné sachant que la machine est sur

32 bits et travaille en complément à 2 pour la représentation des nombres signés. Les chiffres

sont exprimés en base 10. La case mémoire d’adresse 1000 contient la valeur 2147483640

Programme 1

0

4 LOAD D R1 1000

8 ADD Im R1 1

12 JMPO D 20

16 JMP D 8

20 LOAD Im RB 0

24 STORE B R1 0

Exercice 3. Exécution d'instructions machine

ARCHITECTURE 1 BUS

- Tous les registres sont de 32 bits,

- les instructions sont de format 32 bits

- Le compteur ordinal donne l' adresse du 1er octet de l' instruction

- le temps de cycle mémoire = un temps cycle horloge

- On appellera LEC et ECR les commandes lecture et écriture en mémoire(RAD registre

adresses mémoire et RDO registre de données). INCO permet l'incrémentation du CO.

Donnez le chronogramme d'exécution de l'instruction

ADD direct R3 champ2

RI

CO

RAD

RDO

R0

R6

UAL

Y

Z

ARCHITECTURE 2 BUS

On exécute sur l'architecture de processeur suivant plusieurs instructions avec des modes

d'adressage différents :

ADD Im R2 valeur : addition de R2 et de l'opérande valeur obtenu par adressage

immédiat et stockage du résultat dans R2

LOAD I R3 champ2 : chargement de R3 avec un opérande obtenu par adressage indirect.

6

6

7

7

1

/

7

100%