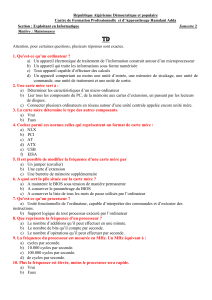

Cours Architecture des ordinateurs 2015/2016 SMI

Architecture des Ordinateurs

Pr. Jamal EL KAFI

Faculté des Sciences

Université Chouaïb Doukkali

El Jadida

L’architecture des ordinateurs ?

Ordinateur =

Machine qui traite une donnée fournie par un

organe d’entrée suivant un programme et

délivre une information sur un organe de

sortie

Architecture =

Conception et organisation des composants

matériels de l’ordinateur

Architecture des Ordinateurs ?

Jeux d’instructions

Applications

Systèmes

D’exploitation

Compilateurs

Processeur E/S

Conception digitale

Circuits

Éléments constitutifs

Un boîtier

Des Cartes (internes)

Carte mère,

Carte réseau,

Carte vidéo …

Des périphériques (internes et externes)

Disques, lecteur de CD, …

Écran, clavier, …

La carte mère

Le chipset : circuits qui contrôlent les

ressources (bus, mémoire, slots, …)

L’horloge et le CMOS

Le BIOS

Le bus système

Les connecteurs d’extension (slots)

La mémoire (cache et RAM)

Le processeur

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

1

/

32

100%