Chapitre 10 Test des Mémoires et des PLAs

1

Chapitre 10

Test des Mémoires et des PLAs

« Programmable Logic Array »

Cours ELE6306

Département de Génie Électrique

École Polytechnique de Montréal

1

ELE6306 – Chap. 10 : Test des mémoires © A. Khouas

Plan

)Les circuits à structures régulières

¾Définition

¾Test des circuits à structures régulières

)Test des mémoires

¾Caractéristiques des mémoires

¾Modèles de fautes

¾Algorithmes de test

)Test des PLA « Programmable Logic Array »

¾Caractéristiques des PLAs

¾Modèles de fautes

¾Algorithmes de test

2

ELE6306 – Chap. 10 : Test des mémoires © A. Khouas

Les circuits à structures régulières

)Définition :

¾Ce sont les circuits composés d’une même structure qui se

répète

Les mémoires

Les PLAs « Programmable Logic Array », CPLD, FPGA

Les parties chemins de données dans les microprocesseurs

)Test des circuits à structures régulières :

¾Inefficacité des méthodes générales

Modèles de fautes

Algorithmes de générations

¾Adaptation de la technique de test aux structures des

circuits

2

3

ELE6306 – Chap. 10 : Test des mémoires © A. Khouas

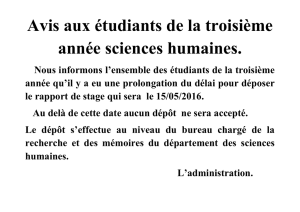

Fabrication des mémoires

Source : Essential of Electronic Testing, Bushnell&Agrawal

4

ELE6306 – Chap. 10 : Test des mémoires © A. Khouas

Structure d’une mémoire

Source : Essential of Electronic Testing, Bushnell&Agrawal

5

ELE6306 – Chap. 10 : Test des mémoires © A. Khouas

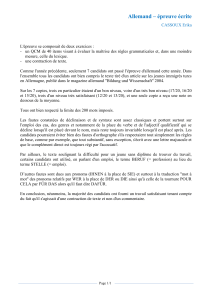

Temps de test vs taille des mémoires

n

1 Mb

4 Mb

16 Mb

64 Mb

256 Mb

1 Gb

2 Gb

n

0.06 s

0.25 s

1.01 s

4.03 s

16.11 s

64.43 s

128.9 s

n .log2n

1.26 s

5.54 s

24.16 s

104.7 s

451.0 s

1932.8 s

1.1 hr

n3/2

64.5 s

515.4 s

1.2 hr

9.2 hr

73.3 hr

24.4 jr

69.6 jr

n2

18.3 hr

12.2 jr

195.5 jr

3127.5 jr

137.1 an

2193.5 an

8774.1 an

Taille Temps de test pour chaque complexité

Temps de test d’une cellule mémoire = 60ns

Source : Essential of Electronic Testing, Bushnell&Agrawal

3

6

ELE6306 – Chap. 10 : Test des mémoires © A. Khouas

Test des mémoires

)La méthodologie de test classique n’est pas efficace

pour tester les mémoires :

¾Plusieurs fautes ne peuvent pas être modélisées par le

modèle de collage

Fautes de voisinages entre les cellules mémoires

Fautes de couplage entre les cellules

¾Les algorithmes classiques de génération ne sont pas très

efficaces

Pas de problème d’activation et de propagation de fautes

Très grand nombre de cellules

Plusieurs vecteurs pour tester une cellule mémoire

7

ELE6306 – Chap. 10 : Test des mémoires © A. Khouas

Modèles de fautes

)Il existe plusieurs modèles de fautes pour les mémoires :

¾Fautes de collage SAF « Stuck-At Faults »

Cellules mémoires et autres composants de la mémoire

¾Fautes de transition TF « Transition Faults »

Cellules mémoires

¾Fautes de couplage CF « Coupling Faults »

Cellules mémoires

¾Fautes d’adressages AF « Adressing Faults »

Lignes d’adressage

¾Fautes de voisinage NPSF « Neighborhood Pattern Sensitive Faults »

Interaction entre les cellules mémoires voisines

¾Fautes (multiples) liées LF « Linked Faults »

8

ELE6306 – Chap. 10 : Test des mémoires © A. Khouas

Fautes de collage « SAF »

Diagramme d’une cellule mémoire

S0 S1

W1

W1

W0

W0

Cellule avec collage @0

S0

W1W0

Cellule avec collage @1

S1

W1W0

Source : Essential of Electronic Testing, Bushnell&Agrawal

4

9

ELE6306 – Chap. 10 : Test des mémoires © A. Khouas

Fautes de transition « TF »

Cellule avec une faute de transition 0 vers 1

S0 S1

W1

W1

W0

W0

Cellule avec une faute de transition 1 vers 0

S0 S1

W1

W1

W0

W0

Source : Essential of Electronic Testing, Bushnell&Agrawal

10

ELE6306 – Chap. 10 : Test des mémoires © A. Khouas

Fautes de couplage « CF »

)Définition :

¾Une faute de couplage entre plusieurs cellules implique qu’une

transition sur l’une engendre un changement sur les autres

En pratique, on limite le nombre de cellules couplées à 2

)Plusieurs types de fautes de couplage :

ªFautes d’inversion CFin:

Une transition sur i engendre une une transition (inversion) sur j

ªFautes idempotentes CFid :

Une transition sur i force la valeur 0 ou 1 sur j

ªFautes dynamiques CFdyn :

Une lecture ou écriture sur i force la valeur 0 ou 1 sur j

11

ELE6306 – Chap. 10 : Test des mémoires © A. Khouas

Fautes de couplage « CF » (suite)

S00 S01

w1/j

w0/i

w1/j

w0/j

w0/i

w0/j

S10 S11

w1/j w1/i

w1/j

w0/j

w1/i

w0/j

w0/i

w1/i

w0/i

w1/i

≺ ==↑ ,ijCFfautelaavecDiagramme in

couplagedefautesDiagramme ans

S00 S01

w1/j

w0/i

w1/j

w0/j

w0/i

w0/j

S10 S11

w1/j

w1/i

w1/j

w0/j

w1/i

w0/j

w0/i

w1/i

w0/i

w1/i

Source : Essential of Electronic Testing, Bushnell&Agrawal

5

12

ELE6306 – Chap. 10 : Test des mémoires © A. Khouas

≺ 1, ==↑ ijCFfautelaavecDiagramme id

Fautes de couplage « CF » (suite)

S00 S01

w1/j

w0/i

w1/j

w0/j

w0/i

w0/j

S10 S11

w1/j w1/i

w1/j

w0/j

w1/i

w0/j

w0/i

w1/i

w0/i

w1/i

Source : Essential of Electronic Testing, Bushnell&Agrawal

13

ELE6306 – Chap. 10 : Test des mémoires © A. Khouas

Fautes d’adressage « AF »

)Définition :

ªles fautes d’adressage modélisent les défauts dans l’adressage des

cellules mémoires

)Plusieurs types de fautes d’adressage :

ªFautes de type 1 :

Une adresse A ne contrôle aucune cellule mémoire

ªFautes de type 2 :

Une cellule mémoire n’est contrôlée par aucune adresse

ªFautes de type 3 :

Une adresse A contrôle plusieurs cellules mémoires

ªFautes de type 4 :

Plusieurs adresses contrôlent la même cellule mémoire

14

ELE6306 – Chap. 10 : Test des mémoires © A. Khouas

Fautes de voisinage « NPSF »

)Définition :

ªUne cellule mémoire peut être affectée par le contenu des cellules

voisines (des combinaisons particulières des cellules voisines)

Ces fautes deviennent très fréquentes avec la diminution des

distances entre les cellules

)Plusieurs types de fautes de voisinage :

ªFautes de voisinage statiques « SNPSF » :

La cellule est collée à une valeur donnée pour une combinaison

particulière des cellules voisines

ªFautes de voisinage passives « PNPSF » :

Une combinaison particulière des cellules voisines empêchent tout

changement sur la cellule

ªFautes de voisinage actives « ANPSF » :

La cellule change quand une des cellules voisines change pour une

combinaison particulière des cellules voisines

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

1

/

17

100%