TP 2 : Modélisation de la consommation d`un bloc - ETIS

Master 2 ESA :

Vers des systèmes reconfigurables

efficaces en énergie…

TP 2 : Modélisation de la consommation d’un bloc matériel via

des mesures réelles

J. Lorandel

Lors de ce TP, l’objectif est de développer un modèle analytique permettant

d’estimer la consommation énergétique d’un bloc matériel. Ce type de modèle

est très pratique car il permet d’estimer directement à haut-niveau, la

consommation d’un bloc matériel en fonctions de paramètres d’intérêt.

fréquence

quantification … Puissance consommée

Taille du filtre = f(freq,quantif,taille de

filtre, …)

Pour développer ce modèle analytique, nous allons devoir réaliser plusieurs

implémentations (i.e. génération de fichiers de configuration du FPGA) de

filtres, où nous allons faire varier la taille et sa fréquence d’horloge. Des

informations supplémentaires seront données par la suite.

Contrairement au TP1 où vous avez utilisé VIVADO, l’environnement de

développement est ISE de Xilinx. Le flot de conception sous ISE comporte les

mêmes étapes mais dans un environnement graphique différent.

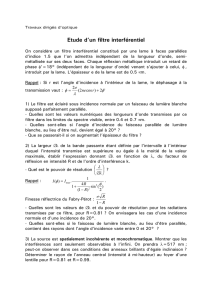

Introduction

•

Objectifs du TP

-Familiarisation avec l’environnement ISE de Xilinx

-Compréhension des étapes du flot de conception Xilinx

-Développement de modèle analytique via des mesures réelles sur

plateformes à l’aide de ChipScope Pro Analyzer

•

Récupération des sources

-Les sources nécessaires au TP sont disponibles ici :

http://perso-etis.ensea.fr/lorandel/M2_ESA.php

Bloc matériel

Récupérer l’archive (TP_Modelling_Student.zip) et extraire les

ressources dans un répertoire en local1.

• Matériel à disposition

-1 Plateforme FPGA ML605

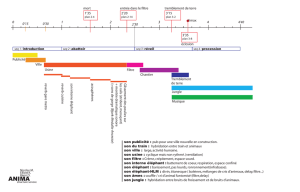

• Déroulement du TP

Sur la figure précédente est décrit les grandes étapes du TP que vous

allez devoir réaliser.

1) Configuration du filtre

Le bloc matériel en question est un filtre FIR. Ce bloc est très utilisé et

on le retrouve dans de nombreux domaines d’application (traitements

d’images, du signal, télécommunications, …). On rappelle l’architecture d’un

tel filtre sur la figure suivante :

Figure : architecture parallèle d’un filtre FIR

1 Attention du chemin du répertoire, il ne doit contenir ni espace ni autres caractères spéciaux !!!

Configuration

du filtre

Synthèse,

Implémentation et

génération du

bitstream

Mesures de

consommation

Création du

modèle

L’architecture peut se décomposer sous la forme de TAP successif dont le

nombre indique la taille du filtre. Pour modifier la taille du filtre, on modifiera

donc le paramètre générique du code VHDL : TAP.

Lors des présentations des intervenants dans l’UE, vous avez pu remarquer

que les données appliquées en entrée d’un circuit pouvait avoir un impact

important sur la consommation. Dans le code VHDL fournit, nous avons

encapsulé le filtre FIR dans une entité supérieure appelée TOP, avec une

mémoire et une PLL. La mémoire est initialisée avec des données à appliquer

en entrée du filtre. L’avantage est de pouvoir appliquer les mêmes données en

entrée du filtre pour les différentes configurations. De cette manière, on peut

s’affranchir de l’impact de la nature des données appliquées. Sur la figure

suivante est illustrée le schéma de principe du système :

LEDs

Switches

La plateforme ML605 dispose de plusieurs périphériques utilisateurs comme

des boutons poussoirs, des switches, des LEDs, …

Nous utiliserons les suivantes pour contrôler le système :

Filtre

FIR

ROM

(génération

des stimuli)

Gestion d’horloge

SW8 -> Clock enable (Activation de la prise en compte de l’horloge)

SW1 à SW5 -> sélection de la fréquence d’horloge :

SW1 -> Fréquence de 10 MHz

SW2 -> Fréquence de 30 MHz

SW3 -> Fréquence de 50 MHz

SW4 -> Fréquence de 70 MHz

SW5 -> Fréquence de 100 MHz

Attention, un seul de ces 5 switches ne devra être à 1, les autres à 0.

La plateforme dispose aussi de LEDs permettant de s’assurer du bon

fonctionnement.

LED_0 (DS12) -> Données écrites en entrée du FIR,

LED_1 (DS11) -> RST

LED_2 (DS9) -> Clock enable

LED_6 et 7 (DS22 et DS21) -> debug

2) Configuration des paramètres du filtre

Dans le dossier fourni, aller dans le répertoire project et double cliquer sur le

fichier project.xise. L’environnement ouvre le projet et vous pouvez observer

l’arborescence du projet via la fenêtre Design. On y retrouve le fichier

TOP.vhd contenant les autres modules VHDL (stimuli_source…).

Ouvrir le fichier TOP.vhd (double clique). Repérer ensuite l’entité du module

TOP. Il possède plusieurs paramètres génériques permettant de modifier la

taille des données (stimuli) d’entrée et de sortie du filtre, le nombre de TAP et

le nom du fichier d’initialisation de la ROM (contenant les stimuli).

Lors de ce TP, on ne modifiera que le paramètre générique TAP

permettant de faire évoluer la taille du filtre. Laisser pour le moment la

valeur 100 par défaut.

• Réalisation du flot de conception

Pour lancer le déroulement du flot de conception, cliquer sur TOP dans la

fenêtre Hierarchy, puis dans la fenêtre Design, double cliquer sur Generate

Programming File. Toutes les étapes du flot de conception allant de la

synthèse à la génération du bitstream vont être réalisées, ce qui peut s’avérer

assez long.

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

1

/

16

100%