ASI - Supélec

Supélec

2ème Année –RENNES

2008 - 2009

TL N°1 Architecture des Systèmes Informatiques (ASI)

RÉALISATION D'UN MICROPROCESSEUR

1. OBJECTIF

Il s’agit de concevoir un processeur simple, de le simuler et d'en faire une réalisation matérielle

(implantation dans un composant programmable de type FPGA) ;

Compte-tenu du temps disponible, le schéma de base du processeur, comprenant les éléments de base et

les chemins de données, est fourni ; le travail consiste alors à définir le séquencement des traitements et

valider le fonctionnement à l’aide d’un programme de test ; il faudra ensuite réécrire un programme plus

optimisé faisant appel à un sous-programme (instruction CALL) de calcul.

2. CARACTÉRISTIQUES GÉNÉRALES

- Processeur à mots de 16 bits et bus adresse de 11 bits (2K mots accessibles).

- Unité de contrôle : compteur ordinal (CO) et pointeur de pile (SP) de 11 bits. Séquenceur câblé.

- Unité de calcul : un accumulateur A de 16 bits et une unité arithmétique et logique (ALU) 16 bits à 8

opérations.

2. INSTRUCTIONS

- Chaque instruction est codée sur un mot de 16 bits.

- Deux modes d'adressage : direct (I = 0) et indirect (I = 1).

- Deux formats d'instructions :

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

codop I Adresse

format 1:

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Adresse

format 2: 1 1 f

0

f

2

f

1

- -

TL1 ASI : Conception d’un processeur ; J. WEISS, le 17 novembre 2008

2

Jeu d'instructions

Notations :

- (X) signifie contenu de X

- X ← Y signifie ranger la valeur de Y à l'adresse X

- AE représente l'adresse effective :

- I = 0 : AE = champ adresse de l'instruction

- I = 1 : AE = contenu du mot dont l'adresse est indiquée dans le champ adresse de l'instruction

Instructions de transfert

codop fonction

LDA

3 A ← (AE)

CO ← (CO) + 1 Chargement accumulateur

STA 0 (AE) ← A

CO ← (CO) + 1 Rangement accumulateur

OUT B (AEpériphérique) ← A

CO ← (CO) + 1 Sortie vers périphérique

Périphériques :

- Afficheur 7 segments : adresse 1 (impaire)

Instructions arithmétiques et logiques

codop fonction

ADD

6 A ← (A) + (AE)

CO ← (CO) + 1 Addition

SUB 5 A ← (A) - (AE)

CO ← (CO) + 1 Soustraction

XOR 4 A ← (A) ⊕ (AE)

CO ← (CO) + 1 Ou exclusif

IOR 1 A ← (A) ∨ (AE)

CO ← (CO) + 1 Ou

AND 2 A ← (A) ∧ (AE)

CO ← (CO) + 1 Et

- -

TL1 ASI : Conception d’un processeur ; J. WEISS, le 17 novembre 2008

3

Instructions de contrôle

Format 1 :

codop fonction

JMP 8 CO ← (AE) Saut inconditionnel

CALL 9 SP ← (SP) - 1

(SP) ← (CO) + 1

CO ← (AE)

Appel de sous-programme

RET A CO ← (SP)

SP ← (SP) + 1

Retour de sous-programme

Format 2 :

(NOP, HLT, Branchements conditionnels)

Branchement : si condition vraie : CO← AE

sinon : CO← (CO) + 1

codop

11f2f1f0 fonction

NOP 11000 Non opération

BG 11001 Saut si plus grand

BZ 11010 Saut si zéro

BGZ 11011 Saut si plus grand ou zéro

BL 11100 Saut si plus petit

BNZ 11101 Saut si non zéro

BLZ 11110 Saut si plus petit ou zéro

HLT 11111 Arrêt

Note : la condition est testée par analyse des indicateurs fournis par l'ALU (Z, P et N) lors de la

dernière opération réalisée

- -

TL1 ASI : Conception d’un processeur ; J. WEISS, le 17 novembre 2008

4

Éléments de base

Unité Arithmétique et Logique (ALU)

L’ALU effectue des opérations sur des opérandes de 16 bits (A et B), fournit le résultat sur 16 bits

et sort 3 indicateurs (Z, P, N) ; l’ALU gère 8 opérations définies par un mot de 3 bits.

Fonction Commande Opération

A 0

A ∨ B 1 OU Logique

A ∧ B 2 ET Logique

B 3

A ⊕ B 4 OU Exclusif

A – B 5 Soustraction

A + B 6 Addition

A + 1 7 Incrémentation

Signification des indicateurs :

Z : résultat nul (= 0)

P : résultat strictement positif (> 0)

N : résultat strictement négatif (< 0)

_______________________________

Accumulateur, Registres et Compteurs

Ce sont des éléments séquentiels, pilotés directement par l’horloge du processeur (sur les fronts

montants). Mis à part le signal de réinitialisation (reset), toutes les commandes sont gérées de manière

synchrone ; tous les signaux de contrôle sont actifs au niveau logique haut ('1') ; les signaux ayant une

fonction "bipolaire" (up_down_sp et rwb (il faut comprendre : Read/Write bar)) réalisent la première

fonction s'ils sont à '1' et la deuxième sinon.

Signification des commandes :

Load : chargement de la donnée présente en entrée dans le registre au front montant d’horloge

suivant.

Cnt : Validation du comptage

Générateur de phases

Un générateur fournit 5 signaux de phases séquentielles d’une durée d’un cycle d’horloge.

Aiguillage des données

Le partage des bus se fait par multiplexage ; il ne doit y avoir qu’une seule entrée de sélection

valide (ces entrées sont dénommées : sel_xxx)

- -

TL1 ASI : Conception d’un processeur ; J. WEISS, le 17 novembre 2008

5

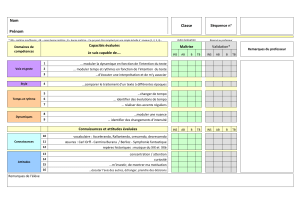

4. Travail à effectuer

Analyse « papier »

Il faut déterminer les différentes phases de fonctionnement du processeur ; pour des raisons de

simplicité, il est conseillé d’aligner toutes les instructions sur le même nombre de phases (5) ; il faut

construire un tableau résumant ces traitements pour tous les types d’instruction. Pour cela, il faut analyser

la disponibilité des ressources (unités et liaisons) du processeur.

Saisie du processeur (Quartus II)

Le projet est disponible sur le réseau du Campus :

//falbala.rennes.supelec.fr/logiciel/electronique/altera/tl_asi_Quartus

Il faut le copier dans un répertoire de travail (de préférence sur disque local).

Le schéma du processeur est fourni, il ne reste qu’à compléter le contrôleur de séquence

(controle), celui-ci est décrit en langage VHDL ; il n’y a pas besoin de connaître en détail la syntaxe du

langage VHDL, il suffit de savoir :

• Une ligne de commentaire commence par 2 tirets (--)

• Toute ligne de code doit se terminer par un point-virgule ( ;)

• Exemple : affectation de la valeur 1 (logique) à VALEUR : VALEUR <= ‘1’ ;

Les bus sont considérés comme des entiers (INTEGER) et les signaux comme des unités logiques

(Std_Logic).

Le fichier (ctrl_template.vhd), fourni en annexe comporte :

Une zone déclarative pour définir les signaux et les constantes (ne rien changer !)

Une zone opérative (process) (qui reste à compléter !)

Nota : il faut sauvegarder le fichier sous un autre nom (contrôle.vhd) avant de faire des

modifications.

Simulation du processeur (Quartus II)

Un programme de test a été placé dans le répertoire (Prog_TL_ASI.mif), sa signification et son

code assembleur sont fournis en annexe.

Simuler le processeur et vérifier son bon fonctionnement

Il est demandé de réécrire le programme de test en utilisant un sous-programme (gestion des

instructions CALL et RET) pour la gestion de la boucle ; il faut pour cela modifier le fichier

Prog_TL_ASI.mif.

Des aides de manipulation du logiciel sont fournis en annexe et disponibles sur le WEB :

http://www.rennes.supelec.fr/ren/fi/elec (rubrique FPGA)

Programmation sur carte de développement DE2

Validation sur la carte (outils d'analyse : SignalTap et Memory Editor)

Réécriture du programme en faisant appel à un sous programme (instruction CALL)

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

1

/

15

100%