TP1 - Free

Architecture des ordinateurs

Daniel Tschirhart - TP Architecture des ordinateurs 1/4

TP architecture des ordinateurs

Rédaction du TP:

Copier le répertoire U:\ArchiOrdi\TP1ARCHI sur votre volume local (H:)

Renommer le document TP1_DOCUMENT_REPONSE.docx présent dans ce répertoire avec les noms du binôme.

Vous rédigerez le compte-rendu du TP avec ce document.

Pour les réponses visibles uniquement sur l’écran de l’ordinateur, faire une capture d’écran (voir annexe 1) et

insérer les images dans votre document.

A la fin du TP, fermer toutes les applications (traitement de texte, éditeurs, …) puis renommer le répertoire

TP1ARCHI avec les noms des binômes et copier celui-ci dans le répertoire U:\ArchiOrdi\ComptesRendu\Groupe.

NE PAS IMPRIMER LA COPIE.

Logiciel utilisé durant le TP:

Les logiciels utilisés dans ce TP sont l'éditeur NotePad++, l'assembleur TASM 5, l'éditeur de liens TLINK et le

moniteur de mise au point TD. Ces commandes s'exécutent dans un environnement 16 bits grâce au mode x86 virtuel

du processeur équipant la machine. Les programmes sont écrits suivant le modèle mémoire TINY dans lequel tous les

registres de segments sont initialisés à la même valeur par le chargeur du système d'exploitation (taille maximale du

programme 64Ki).

Les instructions utilisées dans les exercices sont données à l’annexe 2. Commencer par lire cette annexe.

Nota : il est souhaitable visualiser les extensions des fichiers. Si ces derniers ne sont pas visibles, se rendre dans le

panneau de configurationOption des DossiersAffichage et décocher Masquer les extensions... .

Exercice préliminaire

a) Répertoire SOURCES. Ouvrir une fenêtre de commande dans le répertoire SOURCES (sélectionner le répertoire,

touche et clic droit Ouvrir une fenêtre de commande ici). Assembler le programme modèle par la commande

asm modèle (faire contrôle C à la fin de la commande TLINK (Turbo Link).

La procédure génère les fichiers :

Programme exécutable (taille maxi 64Ki). Il est généré par la commande TLink

Cartographie du code et des données (éditable)

Liste du programme après assemblage (éditable)

Code binaire machine généré par l'assembleur TASM

Contenu du fichier modèle.lst :

Colonne 1 : adresse relative de la donnée ou du code

Colonne 2 : donnée ou code instruction.

o Si l'instruction comporte 3 ou 4 octets les deux derniers octets sont des données ou l’adresse mémoire

sur laquelle porte l'instruction. Le premier octet et éventuellement le deuxième octet représente

l'instruction. Les adresses des instructions de saut (Jxx) sont exprimées en valeurs relatives signées

(fin de l'instruction adresse cible) si le déplacement de la cible du saut est inférieure à +/- 128

octets. Les adresses des instructions d'appel de sous programmes (Call) sont exprimées en valeurs

relatives sur 16bits.

o Si l'instruction est suivie de la lettre r il s'agit d'une adresse recalculée (relocalisée) par l'éditeur de

lien afin de d'allouer correctement la donnée en mémoire

Contenu du fichier modèle.map :

Donne la cartographie du code (class CODE : correspond à .code dans le programme source), des données

initialisées (class DATA, correspond à .data dans le programme source) et des données non initialisées (class

BSS, correspond à .data ? dans le programme source).

Nota : les 256 premiers octets de code sont réservés par le système. La taille effective de votre code est donc

celle données par la classe CODE – 256.

Architecture des ordinateurs

Daniel Tschirhart - TP Architecture des ordinateurs 2/4

Exercice 1

a) Dans le répertoire SOURCES. Ecrire un programme (e1.asm) en langage assembleur x86 effectuant l'opération

suivante sur 16 bits : RES = D1 + D2.

D1 est initialisé avec 1234H et D2 avec 4567H dans la zone initialisée .data. Res est placé dans la zone non

initialisée .data? (voir les syntaxes des déclaration D1, D2 et RES en annexe).

Le code sera placé à partir de DoIt.

Se servir comme base de départ du fichier modèle.asm, puis sauvegarder le sous E1.asm.

b) Ouvrir une fenêtre de commande dans le répertoire SOURCES (sélectionner le répertoire, touche et clic droit

Ouvrir une fenêtre de commande ici). Assembler le programme par la commande asm E1 (faire contrôle C à la

fin de l'assemblage pour ne pas faire l'édition des liens).

c) Editer le fichier e1.lst et E1.map

1. Quelle est la taille totale des données

2. Quelle est la taille totale de votre code

3. Quelle sont les données relocalisées

4. Donner le code de l'instruction Call DoIt. Justifier les deux derniers octets du code de cette instruction.

d) Tester le programme avec la commande dbg e1

1. Donner l'adresse mémoire absolue du programme.

2. Exécuter le programme mode pas à pas (F7) et observer la valeur des registres et des indicateurs.

Exercice 2 : e2.asm

a) Sauvegarder E1.asm sous E2.asm.

b) Quelle est la valeur minimale de D2 qui additionnées à D1 provoque une retenue. Définir cette valeur dans le

programme. Modifier D2 avec la valeur calculée.

c) Assembler (asm e2) puis exécuter (dbg e2) le programme en mode trace pour vérifier votre calcul (observer la

valeur des registres et des indicateurs). Faire une copie d’écran des registres et des indicateurs après l’exécution

de l’instruction Add AX, D2.

Exercice 3

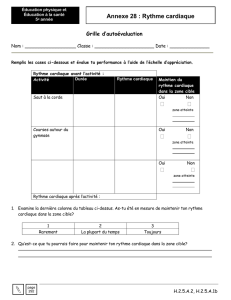

Soit le programme assembleur suivant (nota toutes les données sont en base hexadécimale).

Ce programme initialise la zone mémoire constitué d’un tableau de données 16bits situé à partir de

l’adresse 2000H avec l’entier 16 bits 1.

L’instruction Int 20 arrête le programme. Nota [valeur] ou [registre] indique contenu mémoire pointé (indiqué)

par valeur ou registre.

a) Que fait l’instruction située à l’adresse 0C94:106. Nota : le terme WORD PTR signifie que la donnée transférée

à l’adresse indiquée par [BX] doit être considéré comme un mot de 16bits (BYTE PTR indique un mot pointé de

8 bits). Pour quelle raison faut-il préciser WORD PTR dans cette instruction ?

b) Pour l’instruction située à l’adresse 0C94:10A, justifier le fait que l’on ajoute 2 à BX (au lieu de simplement

incrémenter (ajouter 1 à) BX).

c) Donner la taille en octets de la zone mémoire initialisée.

d) Ecrire un programme E3.asm initialisant à 0 (format 8 bits), une zone mémoire .DATA? de longueur 31 octets.

Déclaration de la zone mémoire : ZONE DB 31 DUP (?)

e) Assembler puis charger le programme en mémoire (asm e3 puis dbg e3).

Mettre un point d'arrêt après l'appel de DoIt (Breakpoint Toggle ou Breakpoint At) puis lancer le programme avec

la commande GO (F9). Faire une copie d'écran de la zone initialisée et la joindre dans votre rapport.

Exercice 4 : E4.asm

a) Enregistrer E3.asm sous E4.asm. Modifier le programme pour qu'il initialise 64 mots de 16 bits avec la valeur 1,

puis additionner les 64 mots de 16 bits adjacents et mémoriser la somme dans la variable 16 bits SOMME située

après la zone initialisée.

b) Assembler puis charger le programme en mémoire (asm e4 puis dbg e4).

Mettre un point d'arrêt après l'appel de DoIt (Breakpoint Toggle ou Breakpoint At) puis lancer le programme avec

la commande GO (F9). Faire une copie d'écran de la zone initialisée et du résultat et la joindre dans votre rapport.

Architecture des ordinateurs

Daniel Tschirhart - TP Architecture des ordinateurs 3/4

Exercice 5 : E5.asm

ZEBRA est une zone mémoire initialisée avec texte suivant.

Déclaration :

ZEBRA DB 'L''OMBRE DU ZEBRE N''A PAS DE RAYURES', 0

Nota : le caractère <'> signifie début ou fin d'un ensemble de

caractères (chaine de caractères). Pour incorporer ce caractère dans la

chaine il faut le doubler.

La fin de chaine de caractère ZEBRA est indiquée par la valeur 0.

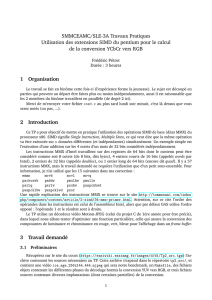

Que fait l'algorithme ci-contre ?

Ecrire le programme correspondant cet algorithme

Remarque : cet algorithme est optimisé pour la vitesse en

minimisant les rechargements du cache du processeur. Justifier cette

dernière remarque.

Assembler le programme et charger le en mémoire.

Visualiser la zone mémoire ou est situé la chaine ZEBRA (faire une

copie d’écran de la zone).

Mettre un point d’arrêt à l’étiquette FIN (F2) et lancer le programme

par le commande GO (F9).

Visualiser la zone mémoire ou est situé la chaine ZEBRA (faire une

copie d’écran de la zone).

On utilisera les instructions suivantes non vues précédemment :

Comparaison de [BX] avec valeur 8 bits

CMP [BX], BYTE PTR valeur

Saut inconditionnel

JMP adresse

Saut conditionnel avec cond = Z, L, G

Format : Jcond adresse

Saut si zéro : JZ adresse

Saut si non zéro : JNZ adresse

Saut si < : JL adresse

Saut si > : JG adresse

Saut si <= : JLE adresse

Saut si >= : JGE adresse

Addition de valeur au contenu de l’adresse pointé par BX

Add [BX], BYTE PTR valeur

Debut

BX = offset ZEBRA - 1

BX = BX + 1

[BX] == 0

[BX] < ‘A’

[BX] > ‘Z’

[BX] = [BX] + 20H

FIN

non

oui

oui

oui

non

non

Architecture des ordinateurs

Daniel Tschirhart - TP Architecture des ordinateurs 4/4

Annexes 1 : comment faire une capture d’écran.

Dans Menu Démarrer/ rechercher taper : Outil Capture. Epingler le raccourci à la barre des taches (clic droit épingler ...).

Annexe 2 : modes d’adressages, éléments de syntaxe de l'assembleur et

instructions du processeur i8086 utilisés dans le TP.

Eléments de syntaxe de l'assembleur

Déclaration d'une donnée 16Bits (ici D1) initialisée avec 0A123H

D1 DW 0A123H ; DW pour 16 bits, DB pour 8 bits

Déclaration d'une donnée 16Bits (ICI RES) non initialisée

RES DW ?

Déclaration d'un tableau (ici TAB) de 256 octets non initialisée

TAB DB 256 DUP (?)

Modes d'adressage

Adressage registre

reg1 reg2.

Exemples: Mov AX, BX ; AX BX

Add AX, DX ; AX AX + DX

And AX, CX ; AX AX & BX

Adressage immédiat

reg1, constante : reg1 constante.

Exemple: Mov CX, 40 ; CX 6410

Adressage mémoire direct

reg1, [constante] : reg1 [constante].

Exemples: Mov CX, [4000] ; CX [4000]

Mov [BX], WORD PTR 1; [BX] 0001

Adressage indirect indexé

reg1, [reg2] : reg1 [reg2].

reg1, [reg2 + constante] : reg1 [reg2 + constante].

Exemples: Mov BX, 2000

Mov AX, [BX] ; AX le contenu du mot mémoire d’adresse 2000H

Add byte Ptr [BX], 20 ; [2000] [2000] + 20H

Ces modes d’adressages s’adressent aux instructions de déplacement, aux opérations logiques et arithmétiques.

Instructions du processeur i8086 utilisés dans le TP

Déplacement de données: Mov

Addition : Add

Comparaison : Cmp

Décrémentation : Dec

Incrémentation : Inc

Saut si zéro : JZ adresse

Saut si non zéro : JNZ adresse

Saut si plus petit : JL adresse

Saut si plus grand : JG adresse

Arrêt de programme : INT 20

1

/

4

100%