Conception d`un régulateur à faible chute de tension 4V, 5mA à

SETIT 2005

3rd International Conference: Sciences of Electronic,

Technologies of Information and Telecommunications

March 27-31, 2005 – TUNISIA

Conception d’un régulateur à faible chute de tension

4V, 5mA à ballast NMOSFET, optimisé pour les

systèmes de télémesures intracorporelles alimentées par

induction magnétique

Francis Rodes*, Olivier Chevalerias*, Eliane Garnier*, Khaled Salmi*, Philippe

Lourenco de Oliveira*, Philippe Marchegay*,Franz Burny **

* ENSEIRB / IXL, Biotelemetry Lab.351 cours de la libération 33405 Talence, France

rodes@enseirb.fr

garnier@enseirb.fr

** Service Orthopédie-Traumatologie, Hôpital Erasme. ULB. B-1070 Belgique.

Résumé: Cet article décrit la conception d’un régulateur linéaire à ballast N-MOSFET présentant à la fois une faible chute de

tension et une grande stabilité. La topologie adoptée est optimisée pour le conditionnement de la tension du secondaire d’une

alimentation par induction magnétique.

Mots clés: Inductive power supply, Low Drop Out (LDO), Voltage regulator,

1 Introduction

Pour télé surveiller les contraintes mécaniques subies

par un implant orthopédique métallique, une méthode

consiste à placer à l’intérieur d’une cavité hermétique

de l’implant, un système de télémesure de contraintes

intracorporelles complet.

Afin d’obtenir, une autonomie illimitée, la

transmission d’énergie et d’informations s’effectue

sans fil par induction magnétique sur une fréquence

porteuse de 125kHz.

Le conditionnement de l’énergie transmise à

l’intérieur de l’implant nécessite alors de recourir à un

régulateur de tension capable de satisfaire les

contraintes suivantes :

- Produire un courant de l’ordre de 5mA sous

une tension de 4V.

- Maintenir la régulation avec une chute de

tension la plus faible possible, de façon à

atteindre une portée de transmission la plus

élevée possible.

- Etre suffisamment rapide pour atténuer les

ondulations de la tension d’entrée à 125 kHz.

- Consommer un minimum d’énergie.

- Pouvoir fournir des surintensités de 12mA.

- Etre stable quelle que soit la charge en sortie.

- Ne pas nécessiter de composants passifs non

intégrables sur ASIC.

En première analyse, le régulateur linéaire

classique avec ballast de type transistor NPN ou

NMOSFET, ne convient pas en raison de la chute de

tension élevée entre l’entrée et la sortie du régulateur.

Celle-ci atteint en effet 1V pour un transistor NPN et

2V pour un MOSFET de type N.

Pour remédier à ce défaut la solution classiquement

envisagée est un régulateur linéaire à faible chute de

tension ou ¨Low Drop Out¨ (LDO) avec un transistor

ballast type transistor PNP ou MOSFET P.

Mais, de même, cette solution souffre de plusieurs

inconvénients qui la condamnent pour l’application

visée. En effet, d’après (Simpson, 1996), (Rincon-

Mora, 1998):

- L’utilisation d’un transistor bipolaire de type

PNP ou MOSFET de type P risque de rendre

le système instable en introduisant un pôle

supplémentaire aux basses fréquences.

- La stabilisation de régulateur nécessite de

connecter sur sa sortie un condensateur de

forte valeur associé à une résistance série.

- Le couple condensateur / résistance série,

n’assure la stabilité que pour un courant de

charge bien déterminé. Si la charge est

variable, la stabilité risque de ne plus être

assurée.

Pour résoudre le problème posé, nous avons été

amenés à concevoir une topologie plus originale

rassemblant les avantages des deux solutions

précitées :

- La stabilité du régulateur linéaire classique

avec ballast de type transistor NPN ou

NMOSFET.

- Un faible chute de tension entrée / sortie.

La solution adoptée consiste à surélever la tension de

SETIT2005

commande du NMOSFET de sorte que celle-ci

n’intervienne plus dans la chute de tension entrée /

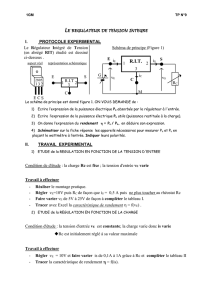

sortie. Le schéma simplifié de ce régulateur est

représenté à la figure 1, son principe est décrit ci-

dessous dans le paragraphe 2.

2 Régulateur type “low drop out” avec

ballast NMOSFET

Le schéma de principe de cette nouvelle topologie

est représenté sur la figure 1. Pour obtenir une

faible chute de tension avec un ballast NMOSFET,

l’idée consiste à surélever la tension d’alimentation

de l’amplificateur d’erreur (A), par rapport à la

tension d’entrée (Vin). La valeur de la surtension à

produire devant être supérieure au V

GS nécessaire

pour assurer la mise en conduction du NMOSFET.

Figure1. Schéma de principe du régulateur à faible chute de

tension avec ballast NMOSFET

Pour générer cette surtension deux techniques

peuvent être employées selon la nature de la

tension d’entrée :

- Si la tension d’entrée est continue (pile,

accumulateur), la seule solution possible

consiste à recourir à une convertisseur à

découpage (à capacités commutées par

exemple).

- Si la tension d’entrée est alternative, la

solution est bien plus simple, puisqu’il

suffit de réaliser un doubleur de tension à

diode et condensateurs (ou générateur de

tensions symétriques), et le placer en

amont du régulateur (voir figure 1).

Une transmission d’énergie par induction

magnétique produisant naturellement une tension

alternative aux bornes de la bobine secondaire (LS),

c’est évidemment la deuxième technique que nous

avons adoptée. C’est ainsi que nous avons abouti au

schéma de principe complet représenté sur la figure

1. Du fait de la présence d’une surtension, et des

contraintes spécifique à l’application, la conception

des éléments qui composent le schéma de la figure 1

présente quelques particularités qui sont décrites

dans les paragraphes qui suivent.

3 L’amplificateur d’erreur et le circuit de

démarrage

La résistance de sortie R

s d’un régulateur

conditionne sa régulation en charge. En effet, plus

cette résistance est faible, plus performant est le

régulateur. L’expression simplifiée de la résistance

de sortie d’un régulateur tel que celui représenté

figure 1 est d’après (Grebene, 1987) donnée par la

relation (1).

( )

+

+

+=

21

2

m

21s

RR R

A1.g

1

//RRZ (1)

gm représente la transconductance du transistor

ballast.

Cette relation montre que pour obtenir une faible

valeur de résistance de sortie, il faut concevoir un

amplificateur d’erreur avec un gain le plus élevé

possible.

En outre, une bonne régulation aussi bien en amont

qu’en aval n’est possible que si la fréquence de

coupure de l’amplificateur d’erreur est supérieure à

la fréquence de la transmission par induction

magnétique (125kHz).

Par ailleurs, l’alimentation de l’amplificateur se fait

sous 12V grâce au doubleur de tension placé en

amont. Or, dans la technologie BiCMOS 0.8µm

d’AMS (AMS, 1995), la tension de claquage de

l’oxyde est de l’ordre de 13V. La marge de sécurité

semble donc très faible, et une étude plus

approfondie de la tenue en tension du circuit

s’avère nécessaire. La figure 2 nous montre que

seuls les puits N et le substrat ont à supporter la

tension maximale du circuit. En effet, le substrat

dopé P se situe au potentiel le plus bas du circuit,

c’est-à-dire la masse pour cette application. Les

puits N, eux, se situent au potentiel le plus élevé

(12V).

Figure 2. Vue en coupe d’un PMOS en technologie AMS

BiCMOS

La tension maximale pouvant être appliquée entre

la couche N+ Well et le substrat P est de 55V (AMS,

1995), celle entre la couche enterrée N+ et le substrat

P est de 33V : il n’y a donc aucune contre-indication

à utiliser une tension de 12V.

La source de courant associée à l’amplificateur est

représentée sur la figure 3. La source de courant elle-

même est composée des transistors Q1 à Q4 et de la

résistance R

1. Dans cette structure, la résistance R

2

sert à la polarisation de la source de courant. Sur la

figure 4, cette source de courant est symbolisée par le

générateur de courant I.

SETIT2005

Q2 (1)

R2

Vdd

R1

Q4 (1)

Q1 (N)Q3 (1)

Iref

Figure 3. Schéma de la source de courant

En première approximation l’expression de I est de

la forme:

1

tR)Nln(U

I⋅

=où :q

kT

Ut= (2)

Il n’est pas nécessaire que le courant de référence

soit élevé. En effet, nous utilisons le rapport des

dimensions sur les PMOS M

12 et M

13 (figure 4)

montés en miroirs de courant pour obtenir le

courant désiré dans les différentes branches. Pour

rester dans des dimensions relativement faibles,

nous avons fixé le courant de référence à 4µA. N est

donné par le rapport S

Q1/SQ3 (Figure 3). Pour

minimiser la surface occupée par R1, N est fixé à 2.

V0

I

M3 M4 M7

M8

T5 T6

R5 R6

R1

R2

I1

I

M9 M10

M12

M13 M14

M11

T7 T8

R7 R8

Vout

Amplificateur d'erreur

Circuit de démarrage

Vbg

Vin

2Vin

R10

R9 Ta

Figure 4. Schéma complet de l’amplificateur d’erreur

L’amplificateur d’erreur de la figure 4 est constitué

de deux étages de gain. La paire différentielle en

entrée du premier étage (M9, M10) est de type

PMOSFET afin d’obtenir une grande résistance

d’entrée. Pour réduire le bruit, on utilise deux

transistors en parallèle avec un rapport W/L

important. Ceci permet d’obtenir un gain élevé ainsi

qu’une fréquence de coupure de l’ordre de 500kHz.

Avec cet étage d’entrée, le gain obtenu en

simulation est de 48dB avec un courant

d’alimentation ne dépassant pas 40µA. La fréquence

de coupure est proche de 500 kHz avec des temps

de montée et de descente de l’ordre de la µseconde.

Le second étage constitué d’une simple source

commune (M11) a un gain de 23dB pour une

consommation de 31 µA. L’excursion en sortie est

limitée d’une part au niveau bas par le V

ds du

NMOS (M11), et d’autre part au niveau haut par le

Vds du PMOS (M14) monté en source de courant.

(Ce dernier limitant le niveau haut à : 2Vin-Vds. Les

différents temps de montée, de descente et de

propagation de l’amplificateur sont inférieurs à 500

ns.

La tension de référence de type bandgap étant

alimentée par la sortie du régulateur, elle ne

fonctionne pas correctement tant que cette tension

de sortie n’atteint pas 4V. Par conséquent, un

circuit de démarrage représenté à la figure 4 a été

ajouté pour produire une tension de référence

même si le bandgap n’est pas à son point de

fonctionnement optimal. En effet, tant que le

bandgap est inférieur à sa valeur nominale, c’est un

circuit diviseur de tension (R9,R10) qui fait office de

référence de tension. Dès que la tension de sortie

atteint une valeur permettant un fonctionnement

correct du bandgap, ce dernier prend la relève et le

fonctionnement normal est rétabli. Avec un

amplificateur d’erreur équipé de ce circuit de

démarrage, un PSRR de 56dB minimum a pu être

maintenu dans le pire des cas.

4 La référence bandgap

Une solution permettant d’obtenir une tension

constante stable en température consiste à faire la

somme de deux tensions à dérives opposées. Ce

principe est à la base de différents circuits, et

notamment les références de Widlar et de Brokaw

(Gray & al, 1982).

Pour notre application, nous avons choisi le

bandgap de Brokaw dont le schéma de principe est

représenté sur la figure 5.

Q1 (1)

Q5

Q2 (N)

R2

R1

Vcc

R3

Q3 (1) Q4 (1)

R4

Vout=Vbg

Vbe1 Vbe2

C1

Figure 5. Référence Brokaw

Le principe de fonctionnement de cette référence de

tension est le suivant :

Supposons que la tension sur la base de Q1

diminue. Dans ces conditions, la différence des

courants dans la paire (Q1, Q2) est ajoutée au

courant de base de Q5 par l'intermédiaire du miroir

(Q3, Q4). Il en résulte une augmentation du courant

de collecteur du transistor Q5 et par conséquent de

SETIT2005

la différence de potentiel aux bornes de la résistance

R4. La tension sur la base de Q1 est ainsi ramenée à

sa valeur initiale. Par conséquent, le circuit

constitue une boucle de rétroaction. La capacité C

1

est ajoutée de façon à stabiliser le système en lui

assurant une marge de phase suffisante.

En négligeant les courants de base, l’équation à

l'équilibre ( III C2C1 == ) s'écrit :

I RVVV 2BE2BE1BE =−=∆

I est le courant de polarisation du miroir (Q3, Q4)

donné par (2), soit :

.ln(N)U = .IRt2

L'expression de Vout fait intervenir BE

V et t

U et

s’écrit

ln(N)

R

R

U2VIR2VV 2

1

tbe1beout ⋅⋅+=⋅⋅+= (3)

En se référant à (Gray & al, 1982) pour le

développement de (3), nous déduisons que la

valeur optimale de Vout pour une température T0

fixée s’écrit :

( ) ( )

0

TTT0g

0

TTbg

out U.EVV =

=α+== (4)

Eg0 est la tension de la bande interdite du silicium et

α un paramètre technologique (α ≈ 2,2).

De cette façon, on peut minimiser les variations de

la tension Vout sur une plage de température en

cherchant à placer l'optimum au milieu de cette

gamme. Dans notre cas, la température normale du

corps étant de 37°C, on obtient 1,12V pour Vout.

Dans la version améliorée de la figure 6, un second

circuit de démarrage est prévu.

Dès que la tension aux bornes de R1 est suffisante,

Q7 se bloque et isole R et Q8 du reste du circuit. Par

ailleurs, des résistances d'émetteur sont prévues

pour Q3 et Q4 afin de minimiser l'effet des

dispersions des transistors PNP. Un miroir de

courant à transistors PNP Wilson accompagné d'un

circuit permettant la compensation de la différence

entre les courants I1 et I2 ont été ajoutés dans le but

d'améliorer la précision.

Q1

Q5

Q2(N)

R1

Vdd

R3

Q3 Q4

R4

Vout=Vbg

R8

Q8

Q7

R

R5 R6

C1

R2

R9

R10

R11

R7

Q9

Q9

I2I1

Figure 6. Schéma complet du bandgap amélioré

5 Résultats et commentaires

Le régulateur a été réalisé en technologie AMS

BiCMOS 0,8µm. Cet ASIC représenté sur la figure 7

occupe une surface de Si ne dépassant pas 2mm2.

Figure 7. Micrographie du régulateur low dropout

La consommation totale du circuit est de 216 µA. La

simulation du bandgap de la figure 6 a permis de

prévoir une tension de référence de 1.19V à 37°C avec

une dérive de 5.6 ppm/°C sur la gamme de

température [25°C- 45°C].

Par ailleurs, la variation de cette tension en fonction

de la variation de la tension d'alimentation V

dd est

de 340 ppm/V sur la plage de variation de

l'alimentation à induction.

Les caractéristiques simulées du régulateur

complet sont données au tableau 1 :

SETIT2005

Vout 4V

Régulation en ligne 49.10-3

Régulation en charge 22mV @ Io = 7mA

?V

out / ?T 90ppm/°C

Vin – Vout @ Iload = 5mA 245mV

I polarisation 240µA

PSRR 56dB

?V

out @ ? Iload = 12mA 140mV

Tableau 1 : Caractéristiques du régulateur

La figure 8 représente la chute de tension simulée

en fonction du courant de charge délivré au circuit

secondaire. Comme nous pouvons le constater sur

cette figure, cette chute ne dépasse pas 245mV pour

un courant de 5mA.

Par ailleurs, le système de modulation produit une

surconsommation de courant de 12mA à chaque

émission de données. Nous avons donc simulé la

chute de tension que provoque une impulsion de

courant d’amplitude 12mA et de durée 15 µS en

sortie du régulateur : Cette chute ne dépasse pas

140mV.

0

25

50

75

100

125

150

175

200

225

250

0 1 2 3 4 5

Is (mA)

Drop-out (mV)

Figure 8. Chute de tension en fonction du courant de charge

Conclusion

Ce travail a montré la possibilité de réaliser un

régulateur linéaire à faible chute de tension au

moyen d’un ballast NMOSFET associé à un

doubleur de tension. Cette topologie présente en

outre une bonne stabilité avec une précision

équivalente à la précision du bandgap qui lui est

associé (340ppm/V). Bien que ce circuit soit dédié à

la régulation de la tension de sortie d’une

alimentation par induction magnétique, son

principe peut être étendu au conditionnement

d’une source de tension continue. Il suffit pour cela

de remplacer le doubleur de tension par un

convertisseur à découpage.

Références

(AMS, 1995) AMS, "0,8µM BiCMOS process parameters",

Austria micro Systems international A.G., 1995

(Gray & al, 1982) P.R. Gray, R.G. Meyer, “MOS operational

amplifier design – a tutorial overview”, IEEE Journal of

Solid-State Circuits, Vol. SC 17, No. 6, pp. 969-982,

December 1982.

(Grebene, 1987) A.B.Grebene, "Bipolar and MOS analog

integrated circuit design", John Wiley & Sons, NewYork,

pp.551-591, 1987.

(Rincon-Mora, 1998) G.A. Rincon-Mora, "A low-voltage,

low quiescent current, low drop-out regulator", IEEE J.

Solid-State Circuits, vol. 33, N°. 1, pp. 36-43, January

1998.

(Simpson, 1996) C. Simpson, "LDO regulators require proper

compensation", Electronic design, pp. 99-104, November

4, 1996.

1

/

5

100%