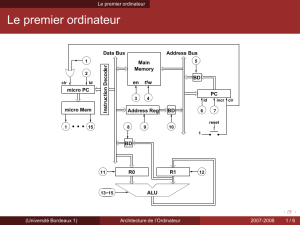

Architecture des ordinateurs

ARCHITECTURE DES

ORDINATEURS

François Médevielle - UPSTI -

Introduction

Découvrir les éléments constitutifs d’un

« ordinateur »

Comprendre l’organisation fonctionnelle

d’une machine

Appréhender l’architecture des

microprocesseurs

Découvrir les critères d’évolution

François Médevielle - UPSTI -

Intel inside… La boîte noire

François Médevielle - UPSTI -

Face avantFace arrière

Port PS/2

Port

parallèle

Port réseau

RJ45

Port Série

COM1

Port VGA

de la carte

vidéo

intégrée

Port USB

Intel inside… La boîte noire

François Médevielle - UPSTI -

Port VGA

Port DVI

DVI-I Dual Link

Port HDMI

La boîte de Pandore?

François Médevielle - UPSTI -

Processeur

et son

ventilateur

Chipset

RAM

Carte

graphique

Disque dur

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

1

/

30

100%