Conception

Objectifs

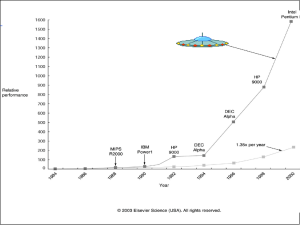

Identifier l’interface entre le logiciel de plus bas niveau et le

matériel

Comprendre la problématique de l’architecture du jeu

d’instruction

Définir deux grandes familles de jeu d’instruction

Quand Monsieur DUPONT exécute un programme !

?

Quand Monsieur DUPONT exécute un programme !

?

Application “Le software”

Hiérarchie

de traduction

?

Application “Le software”

Hiérarchie

de traduction

?Programme en

Pascal, C, C++

C++++++ !!!!...

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

1

/

20

100%