Projet, ELE6306

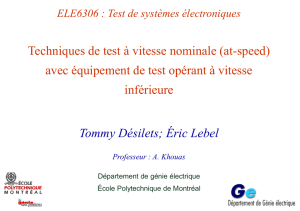

ELE6306 : Test de systèmes électroniques

Projet de cours

Synthèse des algorithmes pour les

générateurs automatiques de vecteurs de

tests (ATPG) pour les circuits séquentiels

Francis St-Pierre ; Olivier-Don Truong

Professeur : A. Khouas

Département de génie électrique

École Polytechnique de Montréal

Projet, ELE6306 - avril 17 École Polytechnique de Montréal

1

Plan

Introduction

Méthode Time-Frame

Algorithme Essential

Algorithme Hitec

Algorithme Atoms

Méthode Séquence d’initialisation

simulation séquentielle basée

Algorithme CONTEST

Algorithme GENTEST

Algorithme ALT-TEST

Comparaison des méthode

Algorithme pour TETRAX MAX ET FAST SCAN

Conclusion

Projet, ELE6306 - avril 17 École Polytechnique de Montréal

2

Introduction

Utilisation des ATPG pour les circuits séquentiels

Différence des ATPG pour les circuits combinatoire et les

circuits séquentiels. Procédure de test différente

Différence et avantage face à la méthode de chaîne de Scan

Il y a deux méthodes utilisées pour les ATPG séquentiels :

Les Time Frames et la simulation séquentielle basée

Projet, ELE6306 - avril 17 École Polytechnique de Montréal

3

Dérouler le circuit dans le temps

Chaque fenêtre (frame) représente le circuit à un moment

différent dans le temps

Faute présente pour chaque fenêtre

Application d’algorithmes combinatoires au circuits

séquentiels

Expension en Time-Frame

Projet, ELE6306 - avril 17 École Polytechnique de Montréal

4

Raisons

5 valeurs logiques ne prenaient pas en

compte la répétition des effets d’une

faute dans un circuit séquentiel

Propagation faute jusqu’à une sortie

primaire, celle-ci sera présente pour

chaque time frame.

Cette façon d’attribuer des valeurs fera

représenter le circuit comme deux

machines qui seront simulées

simultanément par l’ATPG

Besoin d’exécuter cette opération une

seule fois vue qu’elle est effectuée en

même temps dans un time frame

Nine-valued logic

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

1

/

43

100%