vesrsion *

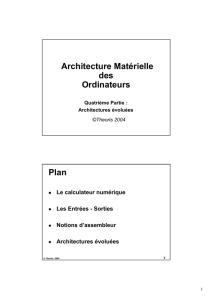

Les moyens vu au chapitre 2 (Techno CISC,RISC,VLIW) ont tous le meme objet, aller plus vite :

Traiter simultanément les bits. Les processeurs ont traité les bits par 12, 18, 24, 32, 60,

64. Les microprocesseurs les traitaient par 8 dans les années 1970, par 16 dans les années 1980, par 32

dans les années 1990, par 64 aujourd'hui. Il ne semble pas que l'on puisse gagner grand chose avec des

mots plus longs, du moins les concepteurs ne l'ont pas tenté. Le mot de 64 bits parait correspondre au

format utile le plus grand.

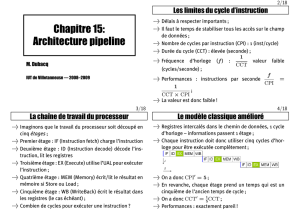

Traiter simultanément les mots. On s'intéresse à deux causes de lenteur. Celle qui est

due au traitement des instructions. Les deux étapes longues sont leur décodage et leur exécution.

Pour leur décodage, on utilise un ou plusieurs pipelines qui tirent parti au mieux de

l'indépendance relative entre les instructions successives.

Pour le traitement, on remplace l'unité arithmétique et logique unique par des opérateurs

spécialisés.

L'autre cause est due à l'alimentation du processeur en mots d'instructions et de données.

On a vu dans le chapitre précédent que la mémoire bon marché est lente, on duplique une partie de son

contenu dans des mémoires plus rapides nommées caches.

Les deux techniques du pipeline et du cache ont été généralisées dans les années 1990.

Traiter simultanément les processus (Cf cours de Mr LELEVE)

Introduction aux pipelines et aux caches

Parmi les prescriptions de Von Neumann, on trouve :

La deuxiéme :

"Le programme et les données sont logés dans une meme mémoire découpée en cellules."

Cette unicité est-elle indispensable ?

Peut-on s'affranchir de cette règle ?

Pour cela, quelles précautions supplémentaires devraient-elles etre prises ?

La cinquième :

"L'exécution de chaque instruction est achevée avant que la suivante soit prise en compte."

On est ainsi certain d'éviter des collisions dommageables.

Peut-on s'affranchir de cette règle ?

Pour cela, quelles précautions supplémentaires devraient-elles etre prises ?

Les deux techniques inventées à cet effet sont illustrées par le schéma suivant.

Le parallélisme spatial consiste à dupliquer les données, soit pour y accéder séparément soit pour utiliser

des mémoires aux caractéristiques meilleures. Ce sont les caches.

Un cache atténue les différences de performances entre deux voisins.

La simultanéité temporelle consiste à décoder par morceaux plusieurs instructions dans le meme temps.

On verra son application au processeur unique. La simultanéité apportée par plusieurs processeurs

travaillant de conserve sera examinée dans les chapitres 10 à 12 (Mr LELEVE). On a nommé ces

structures qui apportent une simultanéité anticipation et recouvrement, plus rarement chaîne

d'assemblage, on dit aujourd'hui pipeline.

Le pipeline augmente les performances du processeur seul.

Pipelines: Origine et principe de fonctionnement.

L'anticipation et le recouvrement sont issus du constat que le chargement d'une instruction et le

début au moins de son décodage ne dépendent pas du résultat de l'exécution de l'instruction précédente,

sauf cas de branchement.

Le mot pipeline est apparu dans les documents du projet STRETCH, lancé à partir de 1956 par

IBM. Les premières réalisations ont été faites dans l'IBM 7030 du projet STRETCH

L'idée première du pipeline est sans obscurité. Une instruction doit etre lue en mémoire, décodée

et exécutée. Il y a là au mois trois étapes, plus encore si l'on décompose certaines d'entre elles. On va

faire en sorte que chaque étape soit traitée dans un étage (slot en anglo-saxon); l'étage précédant traite

l'étape précédente de l'instruction suivante, au lieu d'attendre la fin de l'exécution de l'instruction en

cours.

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

1

/

31

100%