Aucun titre de diapositive

Mémoires embarquées pour les systèmes monopuces - 1

Frédéric ROUSSEAU : TIMA

Mémoires embarquées pour les

systèmes monopuces

Frédéric ROUSSEAU

TIMA 46 Avenue Félix Viallet

38031 Grenoble Cedex France

Tel: +33 476 57 46 41

Fax: +33 476 47 38 14

Email: [email protected]

Mémoires embarquées pour les systèmes monopuces - 2

Frédéric ROUSSEAU : TIMA

Intégration technologique

•Historique [ITRS ’00]

Logic

SRAM

Flash

e-DRAM

CMOS RF

FPGA

MEMS

FRAM

Electro-optical

Chemical Sensors

Electro-biological 98 00 02 04 06 08 10 12

Mémoires embarquées pour les systèmes monopuces - 3

Frédéric ROUSSEAU : TIMA

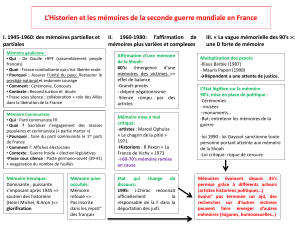

Intégration technologique

•Complexité technologique [ITRS ’00]

Surcoûts

en niveaux de masque

Logique

SRAM

Flash

DRAM

CMOS RF

FPGA

MEMS

FRAM

Capt. chimiques

Electro-optique

Logique

SRAM

Flash

DRAM

CMOS RF

FPGA

MEMS

FRAM

Capt. Ch.

Elec.-opt.

0

0

0

0

0

0

0

0

0

0

1-2

4

4-5

3-5

2

2-10

4-5

2-6

5-8

3-4

3-4

5-9

2-4

3-12

7-14

6-11

9-13

4-16

7-18

4-8

7-10

4-12

6-7

5-11

8-12

5-15

7-10

6-11

9-13

6-15

2-3

6-10

9-12

6-14

7-9 9-15

6-9

4-6

7-9

3-7

6-9

3-4

6-10

3-7 5-7

Mémoires embarquées pour les systèmes monopuces - 4

Frédéric ROUSSEAU : TIMA

Utilisation de la surface de silicium

•Evolution de l ’utilisation surfacique [ITRS ’00]

Area Usage

0%

20%

40%

60%

80%

100%

1999 0,18

µm 2002 0,13

µm 2005 0,1 µm 2008 70 nm 2011 50 nm 2014 35 nm

Mem

Reused

Specific

Mémoires embarquées pour les systèmes monopuces - 5

Frédéric ROUSSEAU : TIMA

Plan de l'exposé

•Quelles mémoires pour les systèmes multiprocesseurs monopuces ?

•Fonctionnement des (S)DRAMs

–Fonctionnement général

–Modes d'accès rapides

–SDRAM et autres

•Améliorations des performances des SoC en utilisant les performances

des mémoires

–Amélioration de la qualité du code des applications

–Relation Mémoire-Architecture-Compilation-Système d'exploitation

•Et les caches ?

•Conclusion

•Bibliographie

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

1

/

39

100%