Méthode de conception - Matthieu ` DonPichol ` Simon

Simulateur de

microcontrôleur

Intel 80C51

Projet de JAVA

Matthieu SIMON

IFITEP3 Juillet 2005

Cahier des charges

Méthode de conception

Cœur

Interface graphique utilisateur

La version 0.2 du simulateur

Le projet avec du recul

8051 Simulator v0.2

Cahier des charges

Architecture 8 bits Intel 80C51.

Gestion des périphériques internes.

Simuler du code assembleur.

Interface graphique : affichage du code source,

des registres et de la mémoire RAM.

Debug.

Composants graphiques externes.

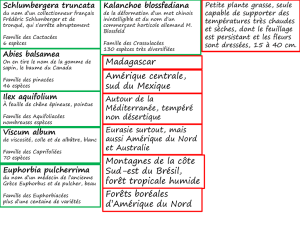

Méthode de conception

Le cœur du microcontrôleur (CORE)

Complètement indépendant.

Représentation logiciel du circuit intégré.

L’interface graphique utilisateur (GUI)

Une et une seule instance du cœur.

Réalise l’« émulation » du circuit logiciel.

CORE

GUI

Méthode de conception : CORE

Charge le code depuis un fichier source

(PARSER).

Possède le jeu d’instruction complet.

L’Unité Centrale de Traitement (CPU) :

Défini les registres et l’espace mémoire.

Phase de simili –assemblage.

Ordonnanceur : récupère, décode et exécute les

instructions.

Gestion des interruptions et des compteurs.

6

6

7

7

8

8

9

9

10

10

11

11

1

/

11

100%