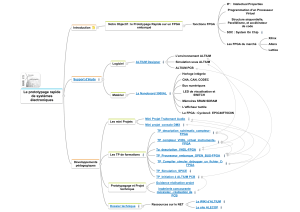

Cas de modélisation d`une application temps réel avec UML

Modélisation UML

d’un Système d’acquisition

Cas d’étude

S. Anvar

CEA / DAPNIA

2

Photomultiplicateur

Photomultiplicateur

Schéma de principe

µ

ϕPhotomultiplicateur t

V

Protocole série

propriétaire

Max 20 Mb/s

Bus A32/D32

40 MHz

Ethernet

Station

de Travail

Ethernet

SDRAM

CPU

Acquisition

Horloge de

référence

20 MHz (REFCLK)

Intégrateur/

Numériseur

(ASIC)

Intégrateur/

Numériseur

(ASIC)

Intégrateur/

Numériseur

(ASIC)

FPGA

I/O et interruptions REFCLK

3

Expression du besoin

nDans un but scientifique, un ensemble de 3 capteurs (photomultiplicateurs) détecte de

faibles émissions de lumière dans les abysses dues à la radioactivité.

nChaque capteur génère un signal électrique à partir de la réception d’un photon.

L’intégrale du signal est une fonction croissante de l’énergie du photon. Ce signal est

transmis à un ASIC d’intégration / numérisation (un pour chaque capteur).

nL’ASIC produit sous une forme numérique (train de données de 6 octets) la valeur de

l’intégrale du signal ainsi qu’une étiquette temporelle l’instant d’arrivée du signal.

nLe FPGA assure la lecture des données depuis l’ASIC par un protocole série propriétaire.

Il écrit les données en mémoire SDRAM selon une logique de type «buffer circulaire ». Il

y a un buffer par PM.

nToutes les 10 ms, le FPGA interrompt le processeur et définit ainsi une « trame» de

données par PM. Des registres du FPGA visibles dans l’espace d’adresse du processeur

fournissent la longeur des trames.

nLe processeur d’acquisition retransmet ensuite ces données à travers un réseau Ethernet

à une station de travail dédiée au traitement et stockage des données.

4

Contraintes

nComme dans la plupart des projets, l’accent doit être mis la simplicité

et la minimisation des efforts de développement (réutiliser l’existant

quand c’est possible)

nLe taux de photons reçu par chaque capteur peut fluctuer fortement

en raison de la bioluminescence des abysses.

nLe FPGA doit être reprogrammé par le CPU Acquisition après chaque

extinction du système depuis un système de fichiers.

nLe système électronique implanté dans le FPGA doit être initialisé par

le CPU Acquisition avant le lancement de l’application

5

Questions (1) : Modèle fonctionnel abstrait

nFaire les diagrammes d’instance / collaboration faisant intervenir les

différents objets du système. Spécifier des appels d’opérations

synchrones et asynchrones sans se soucier des mécanismes

d’implémentation.

nObjets hardware (non analogiques)

nObjets actifs

nObjets passifs

nAppels synchrones et asynchrones d’opérations entre objets

nFaire les diagrammes de classe obtenus par abstraction des

diagrammes précédents

nOrganiser les classes en paquetages pertinents

nFaire les diagrammes de séquences spécifiant la production, le

formatage et l’envoi des données ainsi que le contrôle de flux

6

6

7

7

1

/

7

100%