Mémoires mortes et logique programmable

F. Touchard Cours Architecture ESIL Département d'Informatique 1ère année 2006-2007 1

Mémoires mortes et

logique programmable

F. Touchard Cours Architecture ESIL Département d'Informatique 1ère année 2006-2007 2

Mémoires mortes

on vient d'étudier les mémoires vives

accessibles en lecture et en écriture

mais volatiles

de nombreuses applications demandent de pouvoir

conserver des informations, même si l'alimentation

électrique est coupée

mémoires mortes, le plus souvent accessibles en

lecture seulement

ROM (Read Only Memory)

les informations stockées ne peuvent être modifiées, ni

intentionnellement ni accidentellement

accès généralement très rapide

F. Touchard Cours Architecture ESIL Département d'Informatique 1ère année 2006-2007 3

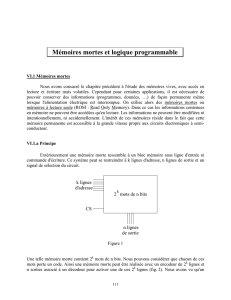

Mémoires mortes

principe

bloc mémoire sans lignes d'entrée ni commande

d'écriture

2k mots de n bits

k lignes

d'adresse

n lignes

de sortie

CS

F. Touchard Cours Architecture ESIL Département d'Informatique 1ère année 2006-2007 4

Mémoires mortes

chaque mot peut être considéré comme un code et la

mémoire réalisée avec un encodeur de 2k lignes et n

sorties associées à un décodeur pour activer une de

ces 2k lignes

F. Touchard Cours Architecture ESIL Département d'Informatique 1ère année 2006-2007 5

Mémoires mortes

exemple d'une mémoire de 4 mots de 4 bits

réalisation possible

de l'encodeur avec

des diodes

table de vérité

X

1

X

0

Y

3

Y

2

Y

1

Y

0

0 0 1 0 1 0

0 1 1 1 0 1

1 0 0 0 1 0

1 1 1 1 1 1

F. Touchard Cours Architecture ESIL Département d'Informatique 1ère année 2006-2007 6

Mémoires mortes

on préfère le plus souvent une organisation matricielle

une partie de l'adresse identifie les lignes

l'autre partie identifie les colonnes

mêmes remarques pour l'assemblage de blocs

mémoires que pour les mémoires vives

F. Touchard Cours Architecture ESIL Département d'Informatique 1ère année 2006-2007 7

Mémoires mortes

applications des ROMs

stockage de programme dans des systèmes

embarqués

calculatrice

BIOS

machine à laver

conversion de code

exemple de la génération de caractères pour un terminal

ou une imprimante

caractère = matrice de points (1 pour le point à afficher)

chaque ligne de la matrice est un mot de n bits (n = nombre de

colonnes)

peut être stocké dans une ROM à l'intérieur du périphérique

F. Touchard Cours Architecture ESIL Département d'Informatique 1ère année 2006-2007 8

Mémoires mortes

visualiser sur un écran à balayage des caractères

constitués de 8 lignes de 5 points

mémorisation de 8 mots de 5 bits

un compteur permet de balayer périodiquement ces 8 mots

pour les afficher en permanence

pour adresser tous les caractères, on va utiliser leur

code ASCII

code ASCII de N (en hexadécimal) : 4E16 = 10011102

code ASCII de R (en hexadécimal) : 5216 = 10100102

F. Touchard Cours Architecture ESIL Département d'Informatique 1ère année 2006-2007 9

Mémoires mortes

d'où les 8 mots

nécessaires pour

chacune des lignes

de chaque caractère

et leurs adresses

et le schéma de

principe du dispositif

F. Touchard Cours Architecture ESIL Département d'Informatique 1ère année 2006-2007 10

Mémoires mortes

génération de fonction numérique

exemple : sin(x), x [0, /2]

l'intervalle [0, /2] est divisé en N = 2k intervalles, la variable

xi prenant les valeurs centrales :

chacune des valeurs est identifiée par l'indice i, qui peut être

utilisé comme une adresse

si on code dans la cellule mémoire associée à l'adresse i le

nombre

fi = Partie Entière [(2n - 1) sin xi]

on obtient une grandeur proportionnelle à sin xi codée sur la

totalité de la gamme dynamique des n bits

Look-up Table

associée à un compteur et un convertisseur numérique-

analogique : possibilité de génération de signaux périodiques

x

i

=

i1

2

x avec i[0,N1]etx=

2N

F. Touchard Cours Architecture ESIL Département d'Informatique 1ère année 2006-2007 11

Mémoires mortes

génération de fonctions logiques

exemple : pouvoir effectuer une des 8 fonctions logiques

sur 2 variables

f0 (a,b) = a.b

f1 (a,b) = a.b

f2 (a,b) = a.b

f3 (a,b) = a+b

f4 (a,b) = a+b

f5 (a,b) = a+b

f6 (a,b) = ab

f7 (a,b) = ab

facile d'écrire la table de vérité des 8 fonctions par rapport aux 4

combinaisons de a et b, puis de mémoriser les 32 valeurs dans

une ROM:

32 bits

a

b

fi

S

F. Touchard Cours Architecture ESIL Département d'Informatique 1ère année 2006-2007 12

Mémoires programmables par l'utilisateur

PROM

Programmable Read Only Memory

pour éviter d'avoir à demander une fabrication spéciale

des mémoires mortes

coûteux

lent

intéressant pour la phase de développement d'un

produit ou pour de petites séries

F. Touchard Cours Architecture ESIL Département d'Informatique 1ère année 2006-2007 13

Mémoires programmables par l'utilisateur

techniques de programmation

méthode des fusibles

une diode et un fusible à chaque noeud de la matrice

initialement tous les fusibles sont conducteurs et donc tous les

bits sont à 1

la définition des 0 se fait à l'aide

d'un programmateur de PROM

qui est capable de détruire les

fusibles en indiquant l'adresse

du bit du mot à modifier et en

injectant un courant sur la sortie

correspondante

mais la manoeuvre est risquée

pour le circuit...

méthodes des anti-fusibles

aucune connection initialement

F. Touchard Cours Architecture ESIL Département d'Informatique 1ère année 2006-2007 14

Mémoires programmables par l'utilisateur

réalisation de la programmation

méthode des anti-fusibles

on fait fondre un diélectrique dans une zone de faibles

dimensions située à l'intersection de 2 électrodes

1ère électrode en

silicium polycristallin

2ème électrode

réalisée dan un implant

fortement dopé n+

diélectrique constitué de

couches d'oxyde et de nitrure

de silicium

la fusion du diélectrique

entraine la diffusion des

dopants

F. Touchard Cours Architecture ESIL Département d'Informatique 1ère année 2006-2007 15

Mémoires programmables par l'utilisateur

d'autres technologies sont possibles, faisant intervenir

diverses combinaisons électrodes-diélectrique

mais toutes ces technologies sont irréversibles du

point de vue de la configuration de la PROM

F. Touchard Cours Architecture ESIL Département d'Informatique 1ère année 2006-2007 16

Mémoires programmables par l'utilisateur

multi-programmation des PROM

en utilisant des transistors à effet de champ MOS

(Metal Oxyde Semiconductors)

la grille permet d'induire

un canal entre la source

et le drain

une tension positive sur la grille

va attirer les électrons et

repousser les trous

une partie des électrons va se

recombiner avec les trous, créant une inversion de population

induisant un canal n entre les implants de la source et du drain

Le transistor est alors passant

pour programmer le noeud, on fait passer un courant intense

entre la source et le drain. Des électrons acquièrent une énergie

suffisante pour atteindre la grille flottante où ils sont piégés.

Quand la charge piégée est suffisante, elle masque le champ

induit par la grille et le transistor est bloqué de façon permanente

F. Touchard Cours Architecture ESIL Département d'Informatique 1ère année 2006-2007 17

Mémoires programmables par l'utilisateur

pour "déprogrammer" le circuit, il faut décharger la

grille flottante

exposition aux rayonnements UV pendant quelques

dizaines de minutes

Erasable Programmable Read-Only Memory (EPROM)

par effet tunnel en appliquant des tensions électriques

suffisamment importantes entre la grille, la source et le

drain

action plus rapide et sans être obligé de retirer le circuit

du système où il est monté

Electrically Erasable Programmable Read-Only Memory

(EEPROM)

le cycle d'écriture d'une EEPROM est environ 1000

fois plus lent que celui d'une RAM

les temps d'accès en lecture des RAM, ROM, EPROM,

EEPROM sont comparables

F. Touchard Cours Architecture ESIL Département d'Informatique 1ère année 2006-2007 18

Mémoires programmables par l'utilisateur

NOVRAM (Non volatile RAM)

EEPROM associée à une RAM. Sert à sauvegarder

rapidement (< 10ms) le contenu de la RAM en cas de

coupure de courant

mémoires flash

EEPROM dans laquelle on peut atteindre plusieurs

cellules en parallèle (octet ou mot), diminuant

sensiblement les temps d'accès en écriture

l'effacement ne peut se faire que par bloc

on trouve maintenant des circuits pour lesquels on

mesure la quantité d'électrons piégés dans la grille

flottante, permettant ainsi de stocker plusieurs bits

dans une même cellule

F. Touchard Cours Architecture ESIL Département d'Informatique 1ère année 2006-2007 19

Réseaux logiques programmables

la famille des circuits logiques programmables (PLD)

est vaste et variée

PAL, SPLD, EPLD,

CPLD, FPGA

exemple d'une PROM

de 16 mots de 4 bits

4 entrées pour les

portes ET

connexions figées

16 entrées pour les

portes OU

connexions program-

mables

F. Touchard Cours Architecture ESIL Département d'Informatique 1ère année 2006-2007 20

Réseaux logiques programmables

Programmable Array Logic (PAL)

matrices des connexions

OU figée

matrice des connexions

ET programmable

6

6

7

7

1

/

7

100%