TD5 : Exécution conditionnelle des instructions

Université Paris Sud D. Etiemble

Master d’Informatique (M1) 2004-2005

1

TD5 : Exécution conditionnelle des instructions

On examine dans ce TD des jeux d'instructions où l'exécution de toutes les instructions sont

conditionnelles.

Soit le jeu d'instructions ARM dont les instructions essentielles sont données en annexe. Toutes

les instructions sont à exécution conditionnelle, en fonction du contenu du registre code

condition : INSTcond, où INST est l'instruction, et cond est la condition (GT, GE, EQ; NE, LT,

LE…).

Dans l'implantation XScale (Intel), les mauvaises prédictions de branchement coûtent 4 cycles.

La prédiction statique est NP pour les branchements avant et P pour les branchements arrière.

Exercice 1 : si… alors… sinon

Q 1 : Donner les versions ARM avec et sans branchements pour l'exécution du code, avec le

nombre de cycles correspondants

int x[N], xmin, xmax;

int i;

xmin=x[0];

xmax=xmin;

for (i=1; i<10, i++)

{

if x[i] <xmin

xmin= x[i];

if xmax < x[i]

xmax=x[i];

}

Q 2 : Donner les versions ARM avec et sans branchements avec le nombre de cycles

correspondants

int a, b, c, d, e, f

if (a==0) { a++, b++, c++, d++, e++}

else (a--, b--, c--, d--, e--}

Q 3 : Etablir la formule qui compare les temps d'exécution des versions avec et sans

branchement pour l'expression

if (cond) {if_bloc}

else {else_bloc}

où N1B est le nombre de cycles pour exécuter {if_bloc} en utilisant des branchements

N2B est le nombre de cycles pour exécuter {else_bloc} en utilisant des branchements

P1 est le pourcentage d'exécution du {if_bloc}

P2 est le pourcentage de mauvaise prédiction de branchement

N1C est le nombre de cycles pour exécuter {if_bloc} en utilisant les instructions

conditionnelles en supposant la condition vraie

N2C est le nombre de cycles pour exécuter {else_bloc} en utilisant les instructions

conditionnelles en supposant la condition fausse

Université Paris Sud D. Etiemble

Master d’Informatique (M1) 2004-2005

2

Exercice 2 : expressions complexes

Q4 : Donner le code ARM pour les fonctions suivantes

a) int foo (int a, int b) {

if (a!=0 && b!=0)

return 0;

else return 1;

}

b) int foo (int a, int b) {

if (a!=0 || b!=0)

return 0;

else return 1;

}

Q5 : Donner le code ARM, puis le code IA-64 pour le programme suivant :

int T[N], a=0, b=0, c=0, d=0, i;

for (i=0; i<N; i++=)

{

if (T[i] <5)

a++;

if ((T[i] >=5)&& (T[i] <10))

b++;

if ((T[i] >=10)&& (T[i] <15))

c++;

if (T[i] >=15)

d++;

}

r1 pointe sur T[0]

r2 contient N

Instructions ARM (extrait)

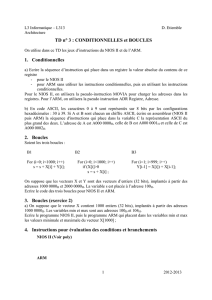

Format des instructions arithmétiques et logiques

31-28 24-21 20 19-16 15-12 11-0

Cond 00 I Code Op S n d Opérande 2

Rs est le registre source (s est le numéro)

Rd est le registre destination (d est le numéro)

Lorsque I =0, opérande 2 est obtenu comme suit

Opérande 2 = rotation à droite de 2 n positions [immédiat non signé sur 8 bits]

Où les 12 bits sont interprétés comme suit

11-8 7-0

Université Paris Sud D. Etiemble

Master d’Informatique (M1) 2004-2005

3

Rotation (2 x n) Immédiat

Lorsque I=1, opérande 2 est obtenu comme suit

Opérande 2 = décalage [Rm]

Où les 12 bits sont interprétés comme suit

11-4 3-0

Décalage (nb de bits) m (numéro de registre)

Les instructions ARM sont définies à la fois pour les formats RR et RI : Opérande 2 = immédiat

ou Rm

Instructions arithmétiques ADD, SUB Rd ← Rs op opérande 2

Instructions arithmétiques ADC, SUBC Rd ← Rs + opérande 2 + retenue

Rd ← Rs - opérande 2 + retenue -1

Instructions arithmétiques RSB, RSC Rd ← opérande 2 - Rs

Rd ← opérande 2 - Rs + retenue -1

Instructions logiques AND, ORR, EOR Rd ← Rs op opérande 2

Instructions de transfert MOV, MVN Rd ← opérande 2

Rd ← complément de opérande 2

Les instructions mémoire sont les suivantes

Instruction Signification Action

LDR Chargement mot Rd ← Mem32(AE)

LDRB Chargement octet Rd ← Mem8 (AE)

STR Rangement mot Mem32(AE) ← Rd

STRB Rangement octet Mem8 (AE) ← Rd

Les modes d’adressage avec la syntaxe assembleur et leur effet sont résumés dans la table ci-

dessous.

Mode Assembleur Action

Déplacement 12 bits,

Pré-indexé

[Rn, #deplacement] Adresse = Rn + déplacement

Déplacement 12 bits,

Pré-indexé avec mise à jour

[Rn, #deplacement] ! Adresse = Rn + déplacement

Rn ← Adresse

Déplacement 12 bits,

Post-indexé

[Rn], #deplacement Adresse = Rn

Rn ← Rn + déplacement

Déplacement dans Rm

Préindexé

[Rn, ± Rm, décalage] Adresse = Rn + décalage

(Rm)

Déplacement dans Rm

Préindexé avec mise à jour

[Rn, ± Rm, décalage] ! Adresse = Rn + décalage

(Rm)

Rn ← Adresse

Déplacement dans Rm

Postindexé

[Rn], ± Rm, décalage Adresse = Rn

Rn ← Rn + décalage (Rm)

Relatif Adresse = CP + déplacement

Instructions de comparaison et branchement

Université Paris Sud D. Etiemble

Master d’Informatique (M1) 2004-2005

4

CMP , TST CMP Rs1, Rs2

TST Rs1, Rs2

Rs1-Rs2 → RCC

Rs1 and Rs2 → RCC

Instructions arithmétiques

avec suffixe S : ADDS, SUBS,

etc

SUBS Rd, Rs1, Rs2 Rd ← Rs1 – Rs2

Positionne Rcc

Bcond (LT, LE, GT, GE, EQ,

NE…)

Bcond, déplacement Si cond, alors

CP ← NCP +déplacement

BL BL déplacement R14 ← NCP

CP ← NCP + déplacement

BLcond BLcond déplacement Si cond, alors { R14 ← NCP

CP ← NCP +déplacement}

Instructions IA-64 : extraits

Chargement compteur de boucle mv lc=valeur lc ←valeur

Branchement boucle Br.cloop L1 ; lc ←lc-1. Branchement si

lc≠0

Chargement mémoire ld rd=[rs], déplacement Rd ←Mem (rs + depl)

Rs ←rs + déplacement

Comparaison (pc) cmp.cond. pi,pj=rs,imm positionne les prédicats

Br.cloop L1 ; ;

1

/

4

100%