Evaluation de la robustesse de circuits intégrés vis-à

*pQpUDOLWpVVXUOHVGpFKDUJHV

pOHFWURVWDWLTXHV

La première partie du document décrit les modèles de tests ESD indispensables en

phase de qualification des structures de protections et des circuits intégrés com-

plexes. Ces tests sont complétés par deux autres modèles moins industriels mais

respectivement capables de caractériser le fonctionnement de composants élémen-

taires et de rendre compte de l’effet du boîtier en termes de tenue aux décharges

électrostatiques.

La partie suivante énonce les phénomènes physiques associés à l’écoulement des

charges électriques dans les composants. Elle prend comme exemple le fonction-

nement d’un transistor GGNMOS (Grounded Gate NMOS) soumis à une ESD et

commente sa caractéristique courant-tension I=f(V). Elle donne également les mo-

des de défaillances spécifiques aux ESD et énumère les techniques d’analyses sus-

ceptibles de les révéler.

La synthèse s’achève par l’étude des méthodes de protection « on-chip » des cir-

cuits intégrés contre les ESD. Des règles sont à respecter pour concevoir des

structures de protection adéquates puis pour les insérer sur le circuit intégré à pro-

téger. Une attention particulière sera réservée aux nouvelles technologies et aux

évolutions qu’elles entraînent.

Pour qualifier la tenue d’un composant aux décharges électrostatiques, il est néces-

saire de disposer de modèles représentant cet environnement hostile dans lequel

évoluent les composants [AMER95][VINS98].

Deux familles de tests sont distinguées dans ce chapitre :

• les tests en qualification ou méthodes de caractérisations normées et couram-

ment utilisées chez tous les fabricants de composants et chez certains équipe-

mentiers,

• les tests d’aide à la conception ou méthodes de caractérisations plus ou moins

bien normées et non encore utilisées de manière systématique par tous les fa-

bricants de composants.

Le modèle du corps humain, HBM (Human Body Model), est le test le plus large-

ment utilisé pour qualifier la tenue des composants aux ESD. Depuis son introduc-

tion dans les années 1980, il a permis de réduire considérablement le taux de dé-

fauts survenus lors de la fabrication puis de l’utilisation des composants.

Le test simule la décharge d’une personne chargée sur un composant électronique.

Le corps de l’opérateur est modélisé par une capacité placée en série avec la résis-

tance de contact de la peau (fonction de la surface de contact de l’opérateur et de

sa résistivité). La sensibilité d’un composant au test HBM est définie par la tension

de charge maximum que le circuit intégré peut supporter sans présenter de dé-

faillance notoire.

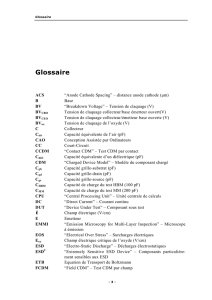

La norme HBM, remise à jour en 1998, décrit [AEC98-a][EIAJ97-a][ESD98] :

• les valeurs de la capacité CHBM (100 pF), de la résistance de contact RHBM

(1,5 kΩ) et de l’inductance LHBM (7,5 µH) (cf. Figure 1. 1),

• la forme de l’onde HBM aux bornes d’un court-circuit ou d’une résistance de

500 Ω (cf. Figure 1. 2 et Tableau 1. 1),

• les valeurs maximales de distorsions en courant autorisées1 [LEE99],

• la classification des composants selon leur niveau de tenue aux impulsions

HBM2.

Pour limiter la durée et les coûts des tests HBM industriels, proportionnels au

nombre de broches des circuits, tout en garantissant une certaine reproductibilité

des mesures, il est conseillé de tester sur un échantillon représentatif :

• chaque broche une par une par rapport aux broches d’alimentation,

• chaque broche d’entrée/sortie une par une par rapport aux autres broches

d’entrée/sortie,

1 Les distorsions de courant sont liées aux capacités et inductances parasites présentes dans les testeurs commerciaux.

2 Classe 1 : composant endommagé par une impulsion HBM inférieure ou égale à 2000 V ; classe 2 : composant qui

fonctionne après un test HBM de 2000 V mais qui ne résiste pas à une impulsion de 4000 V ; classe 3 : composant qui

fonctionne après un test HBM de 4000 V.

• toutes les broches du circuit intégré avec un niveau de tension HBM avant de

passer au niveau de tension supérieur.

La broche la plus fragile détermine le seuil de défaillance du composant.

Les spécifications HBM, données dans les « datasheets » des fabricants, sont mal

détaillées car la procédure de test HBM est mal standardisée. Elle impose que les

circuits intégrés soient de classe 1, 2 ou 3 mais le pas en tension des tests HBM

n’est pas fixé par la norme HBM (il peut être égal ou inférieur à 500 V). Les spéci-

fications ne précisent pas non plus le signe de la tension HBM qui conduit à la dé-

faillance du composant.

3

3 CHBM est la capacité de décharge initialement chargée à la tension HVHBM. Le composant, DUT (Device Under Test), est

testé sur un support adapté aux différents boîtiers électroniques.

0,0

0,5

1,0

1,5

0 50 100 150 200

Temps (ns)

Courant (A)

Ω

Ω

Ω

Ω

Ω

4

Les tests HBM, décrits précédemment, permettent de qualifier les composants en

ESD avant de les monter sur cartes. Lors de leur utilisation, les risques de surchar-

ges électriques EOS doivent aussi être pris en compte. Ils sont générés par des

phénomènes transitoires : surtensions d’alimentation, montages sur cartes électro-

niques, stockage...

Pour modéliser ces surcharges électriques, des tests sont réalisés sur équipements

au moyen de pistolets de décharges conformément à la norme IEC 6100-4-2 ou à

d’autres normes (en fonction du domaine d’application des cartes électroniques).

Ces mesures sont également appelées tests HBM. Il reste pourtant à harmoniser les

méthodologies de test du composant jusqu’au système sur carte car les niveaux de

sévérité des impulsions HBM appliquées sur les circuits intégrés (inférieures ou

égales à 8 kV) n’ont rien avoir avec ceux des décharges appliquées sur les systè-

mes (de 20 à 25 kV par exemple pour les équipements militaires) [AECT91].

La nature des dégradations EOS (seuil de défaillance, localisation) et de leur forme

d’onde (durée, amplitude) est en effet très différente de celles de tests HBM car de

multiples composants parasites de type RLC se trouvent sur le chemin de la dé-

charge [STAN89]. Avec le pistolet, l’amplitude de la décharge HBM que voit le

composant est probablement très inférieure aux 8 kV directement appliqués sur le

circuit intégré.

4 La signification du sigle N/A est Non Applicable. Le courant de pic (en A) à travers 1500 Ω est approximativement

HVHBM(V)/1500 Ω.

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

1

/

26

100%