Le test in-situ relève le défi les technologies basse tension

L

es fabricants de semi-conducteurs

doivent répondre aux demandes du

marché de produits toujours plus

puissants, toujours plus compacts et

présentant une autonomie de fonctionnement

toujours plus longue (donc avec une consom-

mation plus faible,afin de ménager la batterie).

Cela les a conduits, depuis maintenant une

dizaine d’années, à réduire le niveau de la ten-

sion d’alimentation de leurs composants.

En faisant fonctionner les semi-conducteurs

sous des tensions plus basses, la consomma-

tion électrique est plus faible, ce qui permet

aux ingénieurs de conception de réduire les

besoins en ventilation et/ou d’augmenter la

vitesse de traitement. Ce sont ces avantages

qui ont permis de multiplier les perfor-

mances des PC par plus de 400 en l’espace de

18 ans, tandis que leur consommation éner-

gétique demeurait globalement inchangée.

Cela dit, augmentation de la densité des com-

posants et abaissement de la tension d’ali-

mentation vont de pair. Par exemple, pour

la technologie CMOS, plus les structures des

transistors CMOS sont petites, et plus la

couche d’oxyde de la grille est mince. Et plus

elle est mince, plus elle est sensible aux

champs électrostatiques, donc aux tensions

d’alimentation (l’intensité du champ étant

proportionnelle à la tension d’alimentation).

Concrètement, avec une tension d’alimen-

tation de 5 V, il n’était pas possible de des-

cendre à une finesse de gravure inférieure à

0,6 µm, car la fiabilité de fonctionnement

s’en serait trouvée dégradée. Lorsque l’on a

pu maîtriser la technologie de fabrication à

0,35 µm, il a fallu descendre la tension d’ali-

mentation à 2,5Vcc de façon à être sûr que

le composant fonction-

ne correctement.

Tout cela explique la ten-

dance actuelle à la réduc-

tion des tensions d’ali-

mentation. En 10 ans,

celles-ci sont passées suc-

cessivement de 5 V à

3,3V, puis à 2,5V, à 1,8V

et enfin à 0,8V.

Les basses

tensions, un défi

pour le test

Les testeurs in-situ font

appel à des interfaces de

type lit à clous qui per-

mettent aux instruments

de test l’accès électrique

▼

Les circuits intégrés travaillent à des tensions de plus en plus basses (certains fonc-

tionnent aujourd’hui sous 1,2 V, on parle de 0,8 V…) ce qui pose de réels pro-

blèmes lors du test in-situ des cartes incorporant de tels composants. Leur

manque de précision conduit souvent à des erreurs de diagnostic. Mais, surtout,

le courant de forçage trop élevé ou mal contrôlé de ces testeurs peut conduire à

la destruction du composant. Teradyne explique ici le pourquoi du comment et

donne quelques critères sur lesquels il faut plus particulièrement se pencher au

moment du choix d’un testeur in-situ pour technologies basse tension.

53

MESURES 758 - OCTOBRE 2003

L’essentiel

De plus en plus de cartes

électroniques comportent

des composants alimentés

en basse tension, 5 V, voire

moins

Le test de ces cartes pose un

problème aux testeurs in-situ

classiques

Les principaux (destruction

de composants, erreurs de

diagnostic) sont imputables

aux techniques de forçage

mises en œuvre sur ces tes-

teurs

Pour les surmonter, il est

recommandé d’utiliser des

drivers à très basse impé-

dance

TEST DE CARTES ÉLECTRONIQUES

Le test in-situ

relève le défi

les technologies

basse tension

olutions

S

Les testeurs in-situ contrôlent les cartes électroniques en testant un par un

les composants qu’elles comportent.Si la carte comporte des composants basse

tension,le testeur doit en tenir compte,sinon il y a un risque de destruction

de ces composants lors du test…

54 MESURES 758 - OCTOBRE 2003

S

olutions

à chaque nœud ou équipotentielle du cir-

cuit imprimé. Grâce à ces accès, il est pos-

sible de tester individuellement chaque

composant présent sur la carte. Si le test de

chacun des composants est concluant, il y

a une forte probabilité que la carte soit

exempte de défauts d’assemblage et qu’el-

le fonctionnera correctement dans le cadre

de l’application à laquelle elle est destinée.

Cette stratégie de test fait appel à des tech-

niques de désactivation et d’inhibition afin d’iso-

ler le composant sous test des effets élec-

triques indésirables produits par les

composants qui l’entourent.

Pour réaliser le test à vecteurs sous tension

des composants numériques, le testeur uti-

lise des canaux de type driver/sensor (D/S)

capables de forcer les états logiques requis

en entrée et de lire les états logiques résul-

tants en sortie. Les drivers numériques sont

des sources de courant basse impédance

généralement capables de produire ou d’ab-

sorber 600 mA, voire plus. Cette source de

courant force temporairement les nœuds

de la carte aux niveaux logiques exigés par

le test. Cette technique consistant à surali-

menter momentanément les sorties d’un

composant afin de forcer un nœud à son

état logique opposé est connue sous le nom

de “forçage”.

Les techniques de test à vecteurs sont mises

en œuvre avec succès par les équipements

de test in-situ depuis plus de 20 ans. Cela

dit, avec l’arrivée des technologies basse

tension, les testeurs in-situ classiques trou-

vent leurs limites pour réaliser des tests

avec précision, fiabilité et sécurité. Cela

s’explique par le manque de précision des

canaux de test in-situ D/S conventionnels

et par le risque accru d’enfreindre les spé-

cifications de plus en plus serrées des ten-

sions et courants maximum des technolo-

gies basse tension.

Une grande précision des drivers/sensors.

Afin de pouvoir tester les technologies

basse tension, les drivers in-situ doivent

être suffisamment précis pour fournir

les tensions logiques haute et basse

attendues sur les broches d’entrée du

composant. De même, les sensors in-situ

doivent être assez précis pour détecter

la différence entre les niveaux logiques

haut et bas à la sortie du composant.

Les testeurs in-situ classiques utilisent pour

la plupart une configuration D/S associant

un driver élémentaire et un simple compara-

teur. Il s’agit d’une configuration simple,

économique et facile à mettre en œuvre car

elle fait appel à des composants disponibles

dans le commerce. Le driver élémentaire pré-

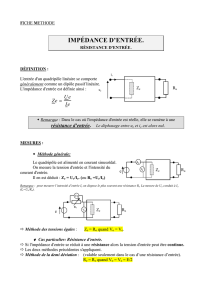

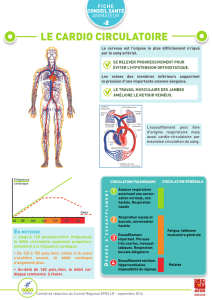

Principe du forçage

Effet de l’impédance trop élevée des drivers

Supposons que N1 ou N2 sont au niveau logique bas, alors le nœud N8 sera au

niveau bas (U3 étant ici une porte ET). Si, pour tester le circuit U8, il est néces-

saire que son entrée 4 soit au niveau haut, le testeur va temporairement injec-

ter un courant sur le nœud N8 de façon à le “forcer” à passer au niveau “haut”.

C’est ce que l’on appelle le forçage.

U8

DUT

U1

U3

N1

N2

N5

N3

N4 N6

N7

N8 4

11

16

U2

driver 1,2 V sans charge

driver 1,2 V avec charge de 6 ohms

Imprécision de la tension de forçage

I.R+décalage

Courant de forçage (mA)

Erreur de tension (mV)

• Le driver haute impédance programmé pour forcer le niveau logique du

composant sous test ne permet en fait d’atteindre que 0,58 V.

• Le driver basse impédance atteint 1,07 V dans les mêmes conditions.

Principe du forçage couramment pratiqué par les testeurs in-situ de façon à forcer les entrées d’un composant numérique au niveau logique

désiré (haut ou bas) pour effectuer le test.

On voit ici l’influence de l’impédance de sortie du “driver”du testeur appliquant le courant de forçage aux composants sous test (afin de les

“forcer”à passer à un niveau logique haut ou bas).Plus ces “drivers”ont une impédance élevée,plus l’erreur sur la tension est importante

(et cette erreur est d’autant plus importante que le courant appliqué est important).Cette erreur peut être très gênante lorsque l’on doit

tester des composants alimentés en basse tension :il est en effet impossible de forcer les entrées du composant au niveau logique désiré par

le test.

55

MESURES 758 - OCTOBRE 2003

S

olutions

sente une impédance de sortie typique d’en-

viron 5 ohms et une erreur de tension sans

charge de l’ordre de 150 mV. Le sensor

employé dans cette configuration se carac-

térise généralement par une erreur de ten-

sion d’entrée qui peut atteindre 300 mV.

Des testeurs in-situ plus performants recou-

rent à une boucle fermée, avec une concep-

tion basée sur des composants “sur mesu-

re”, ce qui améliore grandement la précision

de leurs drivers/sensors. Ces configurations sont

plus coûteuses et sont plus complexes à réa-

liser, mais elles offrent en général une impé-

dance de sortie bien inférieure (1 ohm ou

moins) et une erreur D/S plus faible

(100 mV ou moins).

Chacune de ces conceptions de drivers/sensors

est capable de tester correctement des tech-

nologies fonctionnant sous une tension supé-

rieure à 1,2 V, sans courant de charge. S’il

faut faire du forçage, les testeurs de concep-

tion classique ne sont cependant pas utili-

sables pour des niveaux de tension aussi bas,

à cause de l’impédance relativement élevée

des “drivers” (5 ohms).

Pour des tensions inférieures à 1,2V, le test

devient impossible en raison des impréci-

sions inhérentes au sensor du canal de test.

Un contrôle de la précision lors des for-

çages. Ainsi que nous l’avons déjà dit, on

parle de forçage au cours d’un test in-situ

numérique lorsqu’un driver doit fournir du

courant pour suralimenter temporairement

une sortie de composant dont l’état logique

est l’opposé de celui recherché. Cette situa-

tion se rencontre fréquemment, en raison

de la conception de la carte, d’une défaillan-

ce sur la carte ou de l’oubli d’un code d’iso-

lation dans le programme de test.

Prenons un exemple concret. Un program-

me typique de test in-situ pour une carte

mère de PC a fait apparaître que le forçage a

dû être appliqué lors des tests de des 56 com-

posants numériques, et qu’au total 156 cas de

forçage ont nécessité un courant de forçage

supérieur à 50 mA. La valeur médiane du

courant de forçage s’établissait à 176 mA,

avec un maximum à 600 mA et une durée

maximale de forçage de 2,5 ms.

Un phénomène de forçage de cette ampleur

peut se révéler problématique sur les testeurs

in-situ utilisant un driver à impédance de sor-

tie élevée, du fait que l’imprécision en tension

du driver augmente considérablement avec le

courant de forçage. Ceci se comprend aisé-

ment, il suffit d’appliquer la loi d’Ohm :

U = R.I. Plus le courant de forçage est élevé,

plus la chute de tension dans le driver du tes-

teur est élevée et plus faible est la tension

effectivement appliquée sur la sortie du cir-

cuit intégré. Ainsi, un driver à haute impé-

dance de sortie, programmé pour délivrer

1,2V ne produit que 0,58V sous une char-

ge de 6 ohms. Par contre, un driver à basse

impédance de sortie est capable d’atteindre

1,07V dans les mêmes conditions de char-

ge (6 Ω).

Concrètement, si on prend un driver à

haute impédance standard, pour un cou-

rant de forçage de 100 mA, le driver n’est

plus assez précis pour tester des logiques

1,2V.A 200 mA, il ne peut plus tester avec

précision les technologies 3,3 V. Au-des-

sus de 300 mA, cette précision devient

même insuffisante pour le test de circuits

5V.A 500 mA, le driver à haute impédance

de sortie présente une erreur de plus de

2V. En revanche, le driver à basse impédan-

ce de sortie est suffisamment précis pour

tester une logique 0,8 V même en pré-

sence d’un courant de forçage atteignant

400 mA.

Eviter de détruire les composants

lors du test

En raison de la réduction de la taille des com-

posants et de l’abaissement des seuils de ten-

sion maximum, les technologies basse ten-

sion sont davantage vulnérables à différents

types de défaillances.

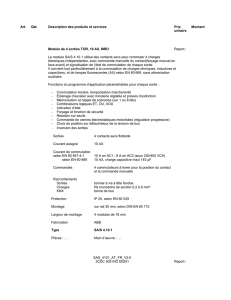

Intel PC Bus Niveau logique

Bus FSB/PSB 1,2 V

AGP 3.0 1,5 V

Interface hub 1,5 V

SRAM DDR 2,5 V

Rambus 1,8 V

Niveaux logiques couramment utilisés par le jeu de composants

Pentium d’Intel sur les cartes mère de PC.

Des forçages mal ajustés

Idéalement, si le driver avait une impédance nulle, la tension de forçage program-

mée serait effectivement appliquée aux points de test. En fait, les drivers présen-

tent une impédance de sortie et ils introduisent une chute de tension proportion-

nelle au courant appliqué. Pour compenser cette chute de tension, la tension de

forçage théorique Vprog est augmentée de 1,2 V à 1,7 V.

Le but est ici de forcer l’entrée du composant U2 sous test au niveau bas, ce qui

nécessite d’appliquer un niveau supérieur à Vih min.

• La tension de 1,7 V à l’entrée du driver produit 1,12 V sur la broche du composant

testé U2 (DUT).

• U2 peut alors être testé car la tension est supérieure à Vih min (0,78 V).

• Il n’y a pas besoin de forçage sur l’entrée U1, donc les 1,7 V programmés donnent

1,6 V sur U1.

• U1 risque d’être endommagé car il subit une tension (1,6 V) supérieure à Vih max.

Pour compenser l’erreur de tension sur le forçage et obtenir le niveau désiré (ici,1,12V),les programmeurs augmentent le niveau de ten-

sion du driver (ici,1,7V).On résout un problème,mais on en crée un autre :en effet,le niveau de tension de forçage appliqué sur le circuit

U1 pour porter son entrée au niveau haut atteint un niveau trop élevé (ici,1,48V),risquant d’endommager le circuit.

Pour éviter ces inconvénients,il faut utiliser des “drivers”à basse impédance de sortie

Humour ? Si les

basses tensions ne

sont pas dangereuses

pour l’homme,elles

peuvent l’être pour

les composants.

Attention donc à ne

pas faire des tests…

destructifs !

56 MESURES 758 - OCTOBRE 2003

S

olutions

Claquage de l’oxyde de grille des transistors

CMOS. Du fait de l’épaisseur réduite de

l’oxyde de grille des transistors, les compo-

sants alimentés en basse tension sont fragiles

lorsqu’ils sont soumis à des surtensions. Le

mécanisme de défaillance est connu sous le

nom de TDDB (Time Dependent Dielectric Break-

down, claquage diélectrique dépendant du

temps) et résulte d’une interaction entre le

temps, la température, la tension et l’épais-

seur de l’oxyde de grille.

Le claquage d’oxyde de grille risque de se

produire lorsqu’une broche de composant

se voit appliquer une tension supérieure à

son maximum nominal. Par exemple, la

tension maximale spécifiée pour le

bus FSB/PSB d’Intel est de 1,75 V. Si les

broches des composants sur ce bus sont

soumises à des tensions supérieures à

1,75 V pendant une durée prolongée,

l’oxyde de grille des transistors s’en trou-

vera endommagé.

La majorité des testeurs in-situ classiques

sont conçus de telle façon que les groupes

de canaux de test D/S doivent partager les

mêmes affectations de niveaux logiques

(les canaux étant groupés par 16 ou 32).

Cette configuration, certes plus écono-

mique, risque toutefois de poser des pro-

blèmes lorsque les canaux D/S d’un même

groupe sont connectés à des broches de

composants fonctionnant sous des ten-

sions différentes. En pareil cas, les pro-

grammeurs n’ont d’autre choix que d’af-

fecter le même niveau logique à tous les

canaux de test du groupe, au risque d’ex-

poser des broches de composants basse

tension à des tensions dépassant leur maxi-

mum nominal.

Par ailleurs, les risques de surtension sont

plus élevés sur des testeurs in-situ

employant des drivers à haute impédance de

sortie car les programmeurs peuvent aug-

menter les tensions de test pour tenter de

compenser les erreurs de tension consta-

tées en cas de forçage.

Des testeurs in-situ plus élaborés évitent

ces problèmes potentiels en utilisant des

canaux D/S plus précis et des drivers dont

les seuils de niveaux logiques peuvent être

programmés indépendamment pour

chaque canal. Cette capacité de program-

mation des tests par canal évite les com-

promis risquant de conduire à appliquer

par inadvertance des tensions supérieures

aux maxima nominaux. De plus, elle garan-

tit que chaque broche du composant sous

test est soumise aux niveaux logiques exacts

exigés par ce dernier.

Surcharge des diodes de protection ESD.

Les circuits intégrés comportent des diodes

de protection contre les décharges élec-

trostatiques. Ces diodes sont sensibles aux

courants de forçage et claquent si celui-ci

dépasse le maximum spécifié. Certains

fabricants de composants conseillent de

ne pas surcharger les diodes ESD au-delà

de 100 mA. Un dépassement de cette limi-

te peut endommager les diodes, ce qui

peut passer inaperçu lors du test de la car-

te (les diodes n’ont aucune incidence sur

le fonctionnement du circuit intégré, elles

n’ont qu’un rôle de protection). Mais ceci

se révélera à l’usage comme étant une

source de problème : en effet, les circuits

intégrés dont les diodes ESD sont endom-

magées ne sont plus protégés contre les

décharges électrostatiques, ce qui peut

dégrader leurs performances et conduire à

une panne de la carte.

Le système de test in-situ TestStation LH

annoncé par Teradyne il y a quelques mois a

été conçu avec l’idée de tester les technolo-

gies à basse tension. Il offre une capacité de

2 048 ou 4 096 points de test, selon les ver-

sions. Le constructeur propose des versions

non multiplexées (un driver/sensor par point

de test) ou multiplexées (1 par 4 ou 1 par 8).

Ce testeur possède une instrumentation

analogique pour réaliser des mesures d’im-

pédance sur les circuits ouverts, les courts-

circuits et les composants passifs (résis-

tances, inductances, condensateurs, etc.). Il

réalise aussi des mesures de temps et de fré-

quence. Pour le contrôle des circuits numé-

riques, il utilise aussi bien des techniques

sans vecteur que des techniques avec vec-

teurs. Le plus grand soin a été apporté à ce

niveau. C’est ainsi que les drivers/sensors

ont une impédance de sortie très faible et

qu’il est possible de programmer le niveau

et la durée des seuils. La précision des sen-

sors est de 45 mV. Ces caractéristiques per-

mettent au testeur de traiter les circuits

électroniques basse tension que l’on trouve

sur de plus en plus de cartes électroniques.

Ce testeur occupe une surface au sol d’à pei-

ne 1,1x0,9 m.

Un testeur étudié pour le test des circuits basse tension

Des surtensions indésirables

• Le testeur fait passer le nœud B

à l’état haut pour éviter le chan

gement d’état de la sortie de U2

pendant le test de U3.

• Du fait de l’activité de la carte

(qui est sous tension), le nœud

A, qui était à l’état haut, passe à

l’état bas, ce qui oblige la sortie du circuit U1 et donc le nœud B, à passer à

l’état haut.

• Comme ce nœud était déjà en cours de forçage à l’état haut, une pointe de

tension survient en B.

• Risque possible de dommage pour les composants U1 et U2 et de faux

messages d’erreur pour U3.

On voit ici les risques de surtension liés à l’utilisation de “drivers”haute impédance,lorsque des sorties changent d’état pendant le forçage.

Les composants U1 et U2 risquent d’être endommagés et on peut avoir des doutes quant à la fiabilité du test du composant U3.

57

MESURES 758 - OCTOBRE 2003

S

olutions

Les testeurs in-situ sont, pour la majeure par-

tie d’entre eux, incapables d’identifier et

d’éviter les surcharges des diodes ESD. Le

Teststation LH de Teradyne offre la capacité de

mesurer les courants de forçage en temps

réel, d’indiquer où se produit le forçage sur

la carte et d’en programmer l’intensité et la

durée maximales.

Latchup des transistors CMOS. Le Latchup

CMOS est une défaillance qui survient lors-

qu’une paire de transistors forme une struc-

ture PNPN ou NPNP de type thyristor. Il en

résulte l’établissement d’un courant élevé,

basse impédance, entre l’alimentation et la

masse du composant, ce qui peut entraîner

son dysfonctionnement, voire sa destruction.

Ce phénomène est généralement provoqué

par l’application d’une brusque montée ou

chute de tension aux entrées du composant

CMOS. Cela peut être dû à une décharge élec-

trostatique ou, durant un test in-situ, au

changement soudain d’état logique d’une

sortie soumise à un forçage.

Pour éviter ces pointes de tension potentiel-

lement dangereuses durant un test in-situ

numérique, il est nécessaire de recourir à des

techniques d’isolation numérique multi-

niveaux (MLDI, Multi Level Disable Inhibit).

Celles-ci permettent de contrôler toutes les

sorties d’un nœud et de s’assurer qu’elles

sont dans un état connu avant d’y connecter

un driver numérique. Certains testeurs in-situ

se bornent à isoler les sorties directement

reliées aux entrées du composant sous test,

mais cela ne suffit pas à prévenir les pointes

de tension se produisant sur les équipoten-

tielles qui ne sont pas directement connectées

à ce composant.

La durée du forçage. Le passage du courant

dans un composant soumis à un forçage

échauffe sa jonction et ses connexions en

sortie. La durée maximale de forçage sans

danger pour un circuit intégré est fonction

du nombre de broches concernées par le for-

çage, du niveau de courant, de la durée, du

type de boîtier et de la technologie du com-

posant. Un forçage excessivement long risque

de causer une défaillance d’une connexion en

cas d’élévation de sa température au-delà de

son point de fusion ou bien de déclencher

sur celle-ci un phénomène de fatigue pou-

vant ensuite réveiller des défauts latents et

entraîner des défaillances prématurées du

composant.

C’est pourquoi il est essentiel que la durée

des tests in-situ soit réduite au minimum

dans les cas de forçage. Certains testeurs

in-situ sont dotés de contrôleurs numériques

spécialisés et de mémoires dédiées à chaque

canal, des architectures qui sont très efficaces

pour appliquer des vecteurs de test avec rapi-

dité et précision. Les testeurs in-situ les moins

performants rallongent la durée des tests car

les vecteurs sont transférés à partir de la

mémoire du calculateur durant le test. La pré-

cision temporelle de ces testeurs est très

imprévisible car elle dépend du type de cal-

culateur utilisé, du volume de données trans-

féré et des autres applications exécutées sur

l’ordinateur.

Une expérience ayant pour but de mesurer

les performances relatives des deux méthodes

a montré qu’un testeur dépourvu de contrô-

leur numérique spécialisé prend 520 fois

plus de temps pour exécuter 1000 vecteurs

de test qu’un testeur qui en possède un (soit

104 ms contre 0,2 ms). Ce gain de temps

permet de moins éprouver les composants

durant un forçage et réduit le risque de

pointes de tension liées à l’activité sur la car-

te.

Les limites d’un test in-situ

classique

Il est clair que les testeurs in-situ classiques ne

présentent pas la précision, la sûreté et la fia-

bilité nécessaires pour tester des technolo-

gies basse tension. Utiliser malgré tout de

tels testeurs ne va pas sans risques.

Réduction de la couverture de fautes. Si les

canaux D/S (drivers/sensors) de test in-situ ne

sont pas assez précis pour piloter et vérifier

les broches basse tension, le fabricant de

cartes peut renoncer à tester les composants

concernés ou bien il doit se replier sur un

test hors tension sans vecteurs (test capacitif

des circuits ouverts ou de jonction de dio-

de, par exemple). Cette alternative n’offre

pas autant d’efficacité que le test à vecteurs

numériques car elle ralentit la cadence de

test, elle augmente le coût et la complexité

des interfaces de test et elle n’est pas en mesu-

re de détecter si on a affaire à une erreur sur

un composant (parce que l’on n’a pas mis

le bon composant) ou à un composant qui

ne fonctionne pas correctement.

Augmentation du risque de faux défauts.

En raison de l’imprécision des drivers et des

sensors des testeurs in-situ classiques et du

rétrécissement de la marge d’erreur entre

seuils logiques haut et bas, le risque est plus

élevé de voir des composants basse tension

indûment signalés comme défectueux. Des

erreurs de diagnostic de ce genre accroissent

les coûts de réparation et entraînent des inter-

ventions inutiles qui risquent d’endomma-

ger la carte davantage encore.

De nouveaux critères de choix pour

le test in-situ

Les fabricants de cartes désireux de tester avec

précision, sécurité et fiabilité les cartes à tech-

nologies basse tension doivent se tourner

vers des équipements de test in-situ réunis-

Des erreurs de diagnostic

• Une faute en U1 (broche d’activation ouverte) cause une situation anormale

de forçage

• Les seuils de tension ne peuvent plus être atteints au nœud N3.

• Le testeur indique que U2, U3 et U4 sont défectueux.

• Rien n’indique que le problème est en fait dû au forçage

Voici une carte défectueuse (circuit ouvert au niveau de U1) pour laquelle un testeur in-situ traditionnel impute incorrectement la faute à

trois composants bons (U2,U3 et U4),tout en laissant passer le véritable problème. Des erreurs de diagnostic de ce genre accroissent les

coûts de réparation et entraînent des interventions inutiles qui risquent d’endommager encore davantage la carte

6

6

1

/

6

100%