DFS : Dynamic Frequence scaling

DFS : Dynamic Frequence scaling

La propriété de DFS est détaillée dans la chapitre2. Dans cette section, la réalisation de DFS et

l’analyse vont être distinguées. La gestion de l’horloge est une approche commune dans la

conception ASIC ou un système basé sur microcontrôleur pour ajustant dynamiquement la

consommation d’énergie. Le FPGA, cependant, cette méthode n’est pas aussi simple en raison de la

structure du réseau d’horloge spéciale. La gestion de la fréquence d’horloge sur FPGA Xilinx est

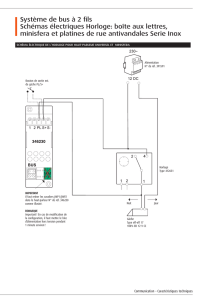

supportée par un composant DCM (Digital Clock Management). DCM est un IP développé par Xilinx. Il

supporte une nouvelle fonction (the Dynamic reconfiguration port DRP) depuis la Virtex-4 FPGA à la

famille Virtex. DRP nous permit de modifier DCM par les commandes externales pour configurer la

fréquence d’horloge. La location de DCM est fixée au milieu du Virtex4 FPGA illustré dans la figure.

Chaque DCM s’occupe deux régions de l’horloge détaillée dans la section précédente. La carte

expérimentale dans notre test conscient 4 DCM. Dans cette figure, le FPGA contient deux DCMs,

chacun est placé dans deux boute de la colonne au milieu de la carte FPGA. La sortie de l’horloge de

DCMs peut être connectée à l’arbre de l’horloge par des buffers de l’horloge.

La fonction DFS dans le FPGA de Xilinx est d’utiliser DCMs à générer des horloges différentes et de

performer l’adaptation dynamiquement de la performance d’exécution. La fonction DFS est vérifiée

premièrement en simulation dans ISE. La contraint de temps de reconfiguration pour générer une

nouvelle fréquence peut être mesure.

La fonction DFS peut être lancée dynamiquement par un microcontrôleur sur puce comme un

MicroBlaze. Cependant, le DRP ne peut pas être connecté directement avec un microprocesseur.

Pour implémenter DFS dans le FPGAs, le système est modifié obligatoirement. Un contrôleur de DFS

est développé d’abord à gérer DFS dynamiquement. Ici, un contrôleur DFS peut être utilisé pour

plusieurs de DCM. Un vu global du système est montré sur la figure. Il est implémenté comme un

périphérique du bus OPB et donc il nous fait facilement gérer la fréquence dynamiquement. Le

protocole de communication entre DFS contrôleur et DCM est présenté dans []. Le signal

« data_MD » dénote la valeur de mulplixeur et la valeur de diviseur. DCM synchronise avec ce

contrôleur par les entrées et reconfigure la fréquence entrée par « dclk_in » et le sorti par

« clk_fx_out ». Des exemples de l’opération de reconfiguration sont présentés dans la table :

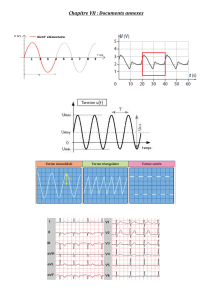

(M,D)

Fréquence généré

2,2

100MHz

4,2

200MHz

6,2

300MHz

1,2

50MHz

Expérimentation de la consommation :

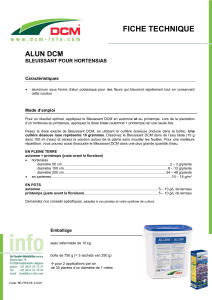

Une tension 5V est appliquée sur la carte expérimentale. La consommation d’énergie est mesurée

pour des différentes fréquences d’horloge du parti fonctionne. La fréquence d’horloge est 100MHz

en défaut. La fonctionnalité basique du système peut être détaille comme la figure3:

Dans le parti statique, un microprocesseur joue comme un contrôleur de reconfiguration. Il connecte

avec un autre processeur par le bus FSL.

Environnement de l’expérimentation :

L’application measurment basée sur Virtex-4 peut être détaille comme un système multi-processeur.

Les expérimentations :

1) La consommation statique : la consommation statique est la consommation de la carte

expérimentale avant la configuration de FPGA. Elle est basée sur les consommations de tous

les périphériques sur la carte expérimentale tels que les mémoires, les LEDs, et les

interconnexions enter tous les composants, etc.

2) La consommation statique + la consommation dynamique sans module fonctionnel : sauf que

la consommation statique, il y a aussi une partie de consommation qui vient des modules

statiques sur FPGA par exemple, le contrôleur de l’adaptation, les mémoires sur puce et les

bus, etc. une autre mesure est fait en ajouter cela comme une consommation stable pour un

système reconfigurable.

3) La consommation globale :

L’analyse des résultats :

1

/

3

100%