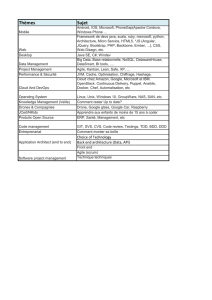

Mise au point de systèmes mixtes et évaluation de puissance : Un

Mise au point de systèmes mixtes et évaluation de puissance : Un exemple

d’application

Anne-Marie TRULLEMANS-ANCKAERT

UCL-DICE, Place du Levant 3, B-1348 Louvain-la-Neuve, Belgium,

[email protected], http://www.ucl.ac.be~anmarie

Résumé

Les outils VHDL-AMS sont particulièrement précieux dans

les applications où l'interaction analogique/digital est critique,

et où l'environnement a une influence sur la fiabilité du

fonctionnement. Un lien transcutané, utilisé dans une prothèse

visuelle, pour transmettre à la fois données et puissance, est

présenté comme exemple, en limitant strictement le niveau de

modélisation aux exigences de précision. La modélisation de

puissance de sous-ensembles critiques aide à comprendre

leur effet sur la consommation globale, et donc à optimiser la

conception. Les résultats de simulation concordent avec les

phénomènes observés sur le prototype expérimental. Un

ensemble de données, testé et validé en transmission via le

lien transcutané, a mis en évidence la récupération correcte

des données, ainsi que les éventuels problèmes de

synchronisation dus au couplage.

Mots Clés: Conception de systèmes mixtes, consommation,

bio-médical.

1. Introduction

La mise au point et la validation de systèmes intégrés

mixtes avant fabrication reste un problème critique,

principalement dans les systèmes à basse

consommation. Les outils VHDL-AMS apportent un

espoir de solution, en particulier avec leurs possibilités

d’écriture d’équations temporelles plus complexes,

faisant intervenir les différents paramètres du système

analysé. Ils seront particulièrement précieux dans les

applications où l'interaction analogique/digital est

critique, et où l'environnement a une influence sur la

fiabilité du fonctionnement. La jeunesse relative de ces

outils fait qu’ils ont été encore peu exploités dans des

situations réalistes, et sans doute jamais dans des

productions industrielles.

Le concepteur de systèmes digitaux complexes dispose

de divers outils efficaces, basés sur les normes Verilog

ou VHDL : outils de simulation, de vérification et

même de synthèse. Le point fort de cette approche est

de permettre de naviguer dans la hiérarchie de systèmes

complexes, depuis le niveau comportemental jusqu'au

niveau des portes logiques, et cela spécifiquement pour

chaque partie du circuit. Le niveau de précision et de

détail s’adaptera à l’évolution de la conception, ou

encore aux nécessités d’une analyse particulière.

Le concepteur de circuits analogiques bénéficie quant à

lui d’outils modernes dérivés de SPICE, dotés de

commandes d'optimisation, d'analyse statistique, …

(environnement ELDO par exemple). La validation des

conceptions est faite au niveau du dispositif, à

condition de disposer de modèles technologiquement

sûrs, fournis par le fondeur. La simulation du système

se base sur la résolution d’équations différentielles,

déduites de modèles plus ou moins évolués des

dispositifs physiques. L’utilisation efficace de ces

outils demande une compétence pointue dans la mise

au point de circuits analogiques.

Le standard VHDL-AMS ajoute à la syntaxe VHDL la

possibilité d’une modélisation par équations

différentielles, donc continue dans le temps, et facilite

la modélisation de systèmes mixtes, tout en gardant les

qualités de modularité et de hiérarchie du langage

original : définition de composant (entité), paramétrage

(generic), architecture spécifique à un niveau de

description .... L’intérêt recherché est la faculté de

réduire la description des éléments non critiques à

l’essentiel de leur comportement, tout en concentrant

l’attention sur les composants critiques.

Nous prendrons comme exemple l'étude d'un lien

transcutané, dont la finalité est l'utilisation dans une

prothèse visuelle, mais qui pourrait être étendu à

d'autres applications. La mise au point de cette

prothèse, menée dans le cadre d'un projet européen,

sous la tutelle de membres de notre laboratoire, ne sera

pas l'objet de cette communication. La fonction du lien

est de transmettre à la fois données et puissance depuis

un dispositif externe, porté par le déficient visuel, vers

un dispositif implanté, qui ne comprend pas de source

autonome de puissance. Il apparaît que le choix de la

modulation des données pour le transfert a un impact

direct sur la fiabilité de la communication, ainsi que

sur l'efficacité en puissance de la transmission. En

outre, le type de codes digitaux transmis, ainsi que le

traitement dans la partie interne, influenceront sa

consommation : consommation à réduire, ainsi que la

dissipation interne, pour limiter l’augmentation locale

de la température, à minimiser pour des raisons de

sécurité médicale.

Une première modélisation [1] de ce système a été

présentée lors des journées FTFC'2001 à Paris, et

analyse le lien à 3 Mbps dans le cas d'une réalisation

basée sur un oscillateur classe E. Nous avons repris ici

une simulation qui représente le lien transcutané

correspondant au premier prototype implanté [2], basé

sur un driver de classe DE, avec la modulation et la

démodulation des données. Les différents modes de

modélisation ont été choisis en fonction des

phénomènes particuliers que l’on désirait mettre en

évidence. Certaines parties sont ainsi modélisées en

VHDL comportemental limité à la pure fonctionnalité,

d’autres en VHDL structurel, d’autres encore par leurs

équations temporelles, ou même simulées par de

simples interrupteurs. Le langage VHDL-AMS, de par

son instruction « break on », est d’ailleurs

particulièrement bien adapté à des systèmes à modèles

variables selon les conditions de fonctionnement. Les

exigences de précision, et donc de temps de simulation,

sont ainsi limitées aux éléments qui les requièrent. La

version de simulateur VHDL-AMS utilisée dans les

tests présentés ici est la version ADVance MS v1.4_1.2

de Mentor Graphics.

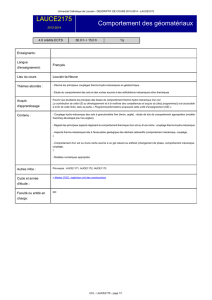

2. Présentation du système

La prothèse visuelle MIVIP-OPTIVIP ([2], [3])

comprend principalement deux modules, un module

externe et un module implanté, reliés par un lien

transcutané formé d’un transformateur spécifique dont

les enroulements sont placés de part et d’autre de la

peau, et qui assure la transmission de la puissance

nécessaire au processeur implanté et des données de

commande des électrodes contrôlant le nerf optique. La

transmission se fait prioritairement de l’extérieur vers

l’intérieur, un retour étant prévu, actuellement sous un

mode half-duplex. Le système externe est basé sur un

processeur complexe qui lit et analyse l’image à faire

reconnaître, et la traduit en une succession

d’impulsions qui sont transmises au processeur

implanté. Celui-ci décode les informations reçues et

active les électrodes branchées sur le nerf optique,

selon une séquence programmable. La transmission des

informations obéit à un protocole complexe codé sur

64 bits, qui assure la synchronisation de la

transmission et la programmation des sources

d’activation des électrodes.

Nous avons limité la modélisation aux éléments situés

au voisinage du transformateur de couplage. Partant

des données, encodées en mots de 64 bits, envoyées

sans interruption en codage Manchester, nous

analyserons le driver de ligne connecté au

transformateur doublement accordé , suivi du

décodage de l’information. Nous tâcherons d’identifier

dans la modélisation les composants les plus critiques,

tant pour le fonctionnement que pour la puissance

dissipée.

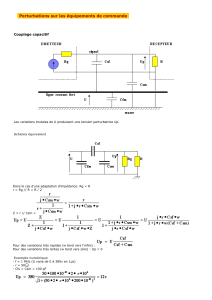

peau

données

à envoyer

codage

Manchester

driver classe

DE

transformateur

à couplage

variable

récupération

d’alimentation

et

démodulateur

données

reçues

VCO

extérieur

intérieur

peau

données

à envoyer

codage

Manchester

driver classe

DE

transformateur

à couplage

variable

récupération

d’alimentation

et

démodulateur

données

reçues

VCO

extérieur

intérieur

Fig. 1 Schéma-bloc du système de transmission

transcutanée de la prothèse visuelle.

La Figure 1 présente le schéma bloc de l’ensemble du

système de transmission en sens direct.

Chaque bloc sera décrit avec le niveau de précision

requis pour mettre en évidence les phénomènes

critiques de son comportement, dans le cadre de

l’analyse recherchée.

Le système complet analysé ici est structuré en

plusieurs blocs principaux (figure 2), qui sont soit

instanciés dans le code sous forme d’entités, soit

directement décrits par des process ou des instructions

simultanées ou concurrentes.

3. Modélisation et simulation des

blocs de base

Bloc 1 : Processeur externe et codage Manchester

(entité MyControl) :

Le processeur externe (processeur spécialisé) génère le

message à transmettre, qui dépend du protocole de

commande de la prothèse. Ce message est composé de

trames de 64 bits, comprenant un header, qui détermine

le type de trame, suivi d’informations spécifiques pour

la programmation des différentes sources d’action sur

le nerf (valeur et synchronisme temporel). Un type

particulier de trame est la trame de synchronisation, qui

assure la cohérence temporelle entre le processeur

externe et le processeur implanté. Dans nos

simulations, ce processeur sera remplacé par un

ensemble de trames enregistrées, à envoyer en

séquence, et sa modélisation en VHDL-AMS peut donc

se satisfaire d’un simple stockage en chaîne de bits à

transmettre*. L’information est traduite en code

Manchester et émise par modulation de fréquence via

un VCO, celui-ci étant simulé directement par la forme

d’onde générée :

entity ClockData is

port(signal F0, FDel,

Vin_a,Vin_b,Vpar_a,Vpar_b : out bit);

end ClockData;

architecture read_data of ClockData is

-- definition des signaux et constantes

signal F0Clock, FDClock : bit := '0';

...

constant F1 : real := 10.8e6; -- fmin

constant TF1 : time := real2time(0.5/F1);

constant F2 : real := 13.2e6; -- fmax

constant TF2 : time := real2time(0.5/F2);

constant TFD : time :=

real2time(1.0/F1 + 1.0/F2);

constant Data_to_send : bit_vector

:= B" ...";

-- vecteur de données test à insérer ici

signal Data_read : bit := '0';

signal DM : bit := '1';

-- data en code Manchester (6Mbits)

begin

...

Gen_FD: process (FDClock)

if Active='1' then

FDClock <= transport not FDClock

after TFD; end if;

end process Gen_FD;

VCO: Process (FDClock)

* On notera qu’il est dommage que la version actuelle

d’ADVance MS ne permette ni lecture de fichiers, ni

stockage en tableau de vecteurs.

-- délais nécessaires au VCO(constantes)

begin

if FDClock'event and FDClock = '1' then

Data_read <= Data_to_send(IData);

if Data_to_send(IData)='0' then

DM <= transport '1', '0' after a4;

F0Clock <= transport '1',

'0' after a1, '1' after a2,

'0' after a3, '1' after a4,

'0' after a5, '1' after a6,

'0' after a7;

else

DM <= transport '0', '1' after b4;

F0Clock <= transport '1', '0' ...;

end if;

if IData < Data_to_send'high then

IData := IData + 1;

else

Active <= '0';

end if;

end if;

end process VCO;

Les signaux de commande du driver classe DE sont

déduits des signaux du VCO :

F0clock Delclock

Vin_a

Vin_b

Vpar_b

Vpar_a

DM

F0clock

F0clock Delclock

Vin_a

Vin_b

F0clock Delclock

Vin_a

Vin_b

Vpar_b

Vpar_a

DM

F0clock

Vpar_b

Vpar_a

DM

F0clock

Fig. 3 Génération des signaux de contrôle du driver

DE et du commutateur synchrone de capacité.

Le signal DelClock est généré par décalage temporel

du signal original F0Clock, et sert à composer les

deux signaux de commande Vin-A et Vin-B qui

assurent le fonctionnement du driver en mode DE :

DelClock <= transport F0clock

after DeadTime; -- delai de N portes

Vin_a <= F0clock and DelClock;

Vin_b <= F0clock or DelClock;

Ce bloc génère également les signaux Vpar_a et

Vpar_b qui contrôlent la commutation d’une

capacité pour la modulation à deux fréquences (voir

Bloc 3) :

Latch: process (F0clock, DM)

begin

if F0clock='0' then

Vpar_b <= not DM;

else

Vpar_a <= DM;

end if;

end process Latch;

Un exemple de signaux générés est fourni à la figure 4.

Dans les deux cas, la modélisation est une

modélisation VHDL classique, proche du matériel,

quoiqu’avec des délais comportementaux (instruction

transport). Aucune modélisation de puissance

n’est faite pour ces parties digitales, qui sont limitées à

la génération des signaux de commande nécessaires

pour activer les blocs critiques.

Fig. 4 Signaux de commande du driver DE et du

commutateur de capacité.

Bloc 2 : Driver classe DE (entité TR_Driver) :

La modulation d’un bit comprend 2 périodes à chacune

des fréquences de base, 10,8 MHz (long = L) et

13,2MHz (short = S). Le bit ‘0’ (code Manchester

‘10’) sera codé « LLSS » et le bit ‘1’ (code Manchester

‘01’) par « SSLL ». L’action sur la ligne se fait par un

driver de classe DE (figure 4), commuté via vin_a et

vin_b à la fréquence produite par le VCO, décrit ci-

dessus, et qui actionne directement le primaire du

transformateur de liaison (figure 5).

Vee

vin_b

vin_a

vl

CT2

Lt

NMOS

PMOS driver DE

vout

Cpar

Vee

vin_b

vin_a

vl

CT2

Lt

NMOS

PMOS driver DE

vout

Cpar

Fig. 5 Driver de ligne de classe DE.

Dans la modélisation, les transistors, qui sont des

transistors MOS de commutation, peuvent être

représentés par de simples interrupteurs, avec une

résistance très faible en conduction (maximum 3Ω),

tandis que les diodes source-substrat ne peuvent être

ignorées : la commutation de la bobine crée en effet

des impulsions importantes, qui mettent ces diodes en

conduction. De même, les capacités des zones de

source sont à prendre en compte (simulées par Cpar

pour les 2 transistors). La modélisation est faite en

VHDL-AMS :

entity TR_driver is

port(terminal Nee, NOUT: electrical;

signal Vin_a,Vin_b : in bit);

end TR_driver;

architecture test of TR_driver is

-- modele switch MOS (N et P)

constant RSon : real := 2.0;

-- resistance fuite diode bulk

constant RDon : real := 26.0;

-- PMOS et NMOS

quantity VPMOS across IPMOS,

IPpar through Nee to NOUT;

quantity VNMOS across INMOS,

INpar through NOUT to electrical_ground;

begin

if Vin_b = '0' use -- PMOS

VPMOS == RSon * IPMOS;

else

IPMOS == 0.0;

end use;

break on Vin_b;

if Vin_a = '1' use -- NMOS

VNMOS == RSon * INMOS;

else

INMOS == 0.0;

end use;

break on Vin_a;

-- diodes fuite

if VPMOS'Above(-0.7) use

IPpar == 0.0;

else

IPpar == (VPMOS + 0.7) / RDon;

end use;

if VNMOS'Above(-0.7) use

INpar == 0.0;

else

INpar == (VNMOS + 0.7) / RDon;

end use;

end test;

Pour analyser le driver DE décrit ici, actionnant le

transformateur couplé doublement accordé, avec la

commutation synchrone de la capacité du primaire, on

observe la tension vl entre l’inductance primaire et sa

capacité, qui est bien sinusoïdale, en concordance avec

la tension de sortie vout du driver (figure 6).

Fig. 6 Simulation du driver classe DE.

La variation d’amplitude observée provient de la

variation de facteur de qualité correspondant à la

variation de fréquence des impulsions de commande.

On notera également que le circuit secondaire est

accordé à une fréquence unique. La modélisation

reproduit fidèlement le comportement quand les deux

transistors sont ouverts : le circuit résonnant étant isolé

du driver, les capacités parasites induisent un début

d’oscillation parasite à chaque commutation,

phénomène observé expérimentalement.

Le driver de classe DE est l’une des parties les plus

gourmandes du système externe. Dans la modélisation

adoptée, le calcul de sa consommation peut se déduire

directement de la consommation sur les sources

d’alimentation, dont la valeur moyenne pour une

simulation donnée peut se calculer par simple

intégration :

quantity Vee across Ialim through Nee

to electrical_ground;

quantity Vcc across Icc through Ncc

to electrical_ground;

Vee == Valim_Vee; Vcc == Valim_Vcc;

power_alim == - Vee * Ialim - Vcc * Icc;

if domain=quiescent_domain use

mean_power == 0.0;

else

mean_power == power_alim'integ / now;

end use;

La puissance consommée sera particulièrement

sensible au delai introduit dans la commande des deux

transistors interrupteurs du driver DE (entre F0Clock

et DelClock). Cette puissance est manifestée par des

pics de courant via les deux MOS de commutation.

Des pics de courant via les diodes du commutateur de

capacité (bloc 3) produisent également des accidents

dans la consommation, mais correspondent à des

puissances faibles (figure 7).

Fig. 7 Pics de courant et puissance du driver classe

DE.

Bloc 3 : Transformateur de couplage doublement

accordé avec commutation synchrone (entités

transfoCT et CT_driver, et modélisation VHDL-

AMS des capacités) :

Le système de transmission entre le module externe et

le module implanté est un transformateur doublement

accordé, dont l’élément transformateur est décrit par

un modèle fonctionnel (Figure 8), qui met en évidence

les inductances des deux enroulements (mesurables) et

le facteur de couplage, qui sera variable en cours

d’utilisation. Ces éléments suffiront pour l’analyse

souhaitée, et sont traduits dans le code VHDL-AMS

suivant :

I1I2

V1+V2+

N1N2

R1R2

L1L2

K

I1I2

V1+V2+

N1N2

R1R2

L1L2

K

Fig. 8 Modèle classique de transformateur.

entity transfoCT is

generic (L1 : real := 1.0e-6

R1 : real := 0.0;

L2 : real := 1.0e-6;

R2 : real := 0.0;

K : real := 0.15);

port (terminal P1, P0, S1, S0 : electrical);

end transfoCT;

library IEEE;

use IEEE.math_real.all;

architecture bhv of transfoCT is

quantity M : real := K * sqrt(L1*L2);

quantity V1 across I1 through P1 to P0;

quantity V2 across I2 through S1 to S0;

begin -- bhv

M == K * sqrt(L1*L2);

V1 == L1 * I1'dot + M * I2'dot + R1 * I1;

V2 == M * I1'dot + L2 * I2'dot + R2 * I2;

end bhv;

Le facteur de couplage est un élément à modéliser de

façon efficace et pratique : c’est lui qui variera en

cours d’utilisation de la prothèse, et il faudra assurer

un fonctionnement aussi peu dépendant que possible de

ce couplage. Pour faciliter l’étude de son influence, le

facteur M a été défini comme une quantity, ce qui

en permet la variation en cours de simulation (voir

plus loin l’étude du couplage).

Les capacités d’accord sont elles directement écrites

dans le système complet, par leurs equations

différentielles, la capacité du primaire étant en fait

commutée entre 2 valeurs, correspondant aux 2

fréquences de la modulation. Une première modulation

à haut niveau en VHDL-AMS de cette commutation a

déjà été présentée [1], sans tenir compte de

l’implémentation sur circuit. Nous avons repris ici une

simulation qui permet de vérifier que les signaux

générés produisent bien l’effet voulu au bon moment.

La commutation est ainsi contrôlée par les signaux

Vpar_a et Vpar_b. Pour assurer une commutation au

moment du passage par 0 de la tension aux bornes de la

capacité, des diodes sont insérées en série avec les

MOS de commutation, qui eux seront simplement

simulés par des interrupteurs, en VHDL-AMS, alors

que les diodes sont modélisées par leur équation

fondamentale :

entity CT_driver is

port(terminal NCT, Ncc: electrical;

signal Vpar_a,Vpar_b : in bit);

end CT_driver;

architecture test of CT_driver is

constant IDS : real := 1.0e-15;

constant VT : real := 0.026; -- ou kT/q/N

quantity Vcc across Ncc to electrical_ground;

quantity VCT across ID1, ID2

through NCT to Ncc;

begin

if Vpar_b = '0' use -- PMOS "on"

ID2 == -IDS * (exp(-VCT/VT) - 1.0);

if Vpar_a = '1' use -- NMOS "on"

ID1 == IDS * (exp(VCT/VT) - 1.0);

else

ID1 == 0.0;

end use;

else -- PMOS "off"

ID2 == 0.0;

if Vpar_a = '1' use -- NMOS "on"

ID1 == IDS * (exp(VCT/VT) - 1.0);

else

ID1 == 0.0;

end use;

end use;

break on Vpar_b, Vpar_a;

end test;

Les différentes capacities sont alors directement

décrites, au niveau de l’interconnexion des entités, par

la definition des quantity et de leurs equations

différentielles :

quantity Vout across ICpar through Nout

to electrical_ground; -- Cpar

quantity VCT1 across ICT1 through Nl

to NCT1; -- CT1

quantity Vl across ICT2 through Nl

to electrical_ground; -- CT2

quantity VCs across ICs through NT2

to NS0; -- capa secondaire

ICT2 == CT2 * Vl'dot;

ICT1 == CT1 * VCT1'dot;

ICpar == Cpar * Vout'dot;

ICs == Cs * Vcs'dot;

Un point particulièrement critique dans la mise au

point du système, et qui a un impact direct sur la

puissance consommée, est la synchronisation des

signaux de commande du driver DE, et du

commutateur de capacité. Une désynchronisation se

manifestera par des pics de conduction des diodes de

substrat, ou par une non cohérence des mises en

conduction des diodes et interrupteurs du

commutateur. La figure 9 montre le cas d’un système

bien synchrone. On y observe les courants des deux

diodes du commutateur, qui s’enclenchent

correctement pour assurer la mise en fonction de la

seconde capacité lors des phases '1' du signal

Manchester.

Fig. 9 Commutation de capacité en synchronisme avec

la modification de fréquence.

Bloc 4 : Ecrêtage et récupération d’alimentation :

Le signal reçu au secondaire du transformateur (partie

implantée de la prothèse) sert à la fois à l’alimentation

de la partie interne, et à la récupération des données. Il

sera donc utilisé pour charger une capacité de balast

interne, et sera mis en forme pour son décodage. Une

6

6

7

7

8

8

9

9

10

10

1

/

10

100%