6 Consommation

Méthodologie de conception des circuits intégrés VLSI - 6. Faible consommation 1/02/10

Olivier Sentieys 1

321

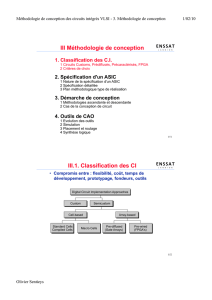

VI Estimation et réduction de la consommation

1. Pourquoi s'occuper de la puissance ?

– Dissipation de chaleur

– Portabilité

– Watt is the problem ?

2. Où partent puissance et énergie électriques ?

– Circuits intégrés numériques

– Microprocesseurs, DSP, ...

3. Comment estimer la consommation ?

4. Comment réduire la consommation ?

– Matériel et logiciel

5. Conclusions

322

1. Introduction

Pourquoi s'occuper de la puissance

dissipée ?

Watt is the problem ?

Méthodologie de conception des circuits intégrés VLSI - 6. Faible consommation 1/02/10

Olivier Sentieys 2

323

Évolutions technologiques

• Famille DEC/Compaq [Herrick99]

• EV4

– 200 MHz @ 3.3V

– 16 gate delays per cycle

– 30W @ 200 MHz & 3.3V

– 1,7 Million Transistors

– 233 mm2

• EV7 (21364)

– > 1000 MHz @ 1.5V

– 100W

– ~100 Million Transistors

– ~350 mm2

• Intel Pentium 4 [Intel 2000]

– 1.5 GHz, 0.18 micron

– Puissance des Pentium suit une courbe exponentielle !

– Réduction de la puissance du P4 par clock gating et power down des unités

fonctionnelles inutilisées

– Une unité thermique embarquée vient couper la CPU si il y a un problème de

refroidissement

– 55 Watts à 1.5 GHz (au lieu de 90 Watts)

• EV5 (21164)

– 350 MHz @ 3.3V

– 14 gate delays per cycle

– 60W @ 350 MHz & 3.3V

– 9,3 Million Transistors

– 298 mm2

• EV8

– > 1-2 GHz (0.125 micron)

– <150W

– ~250 Million Transistors

• EV6 (21264)

– 575 MHz @ 2.2V

– 12 gate delays per cycle

– 90W @ 575 MHz & 2.2V

– 15,2 Million Transistors

– 314 mm2

324

1. Dissipation de chaleur

• Effets indésirables

– Diminution des performances

et de la fiabilité

MTBF/2 pour +10°C

– Augmentation du coût de mise

en œuvre

1€/W si >40W

– Augmentation volume-poids

radiateur, ventilateur, batteries, …

• Evolutions

technologiques ?

Méthodologie de conception des circuits intégrés VLSI - 6. Faible consommation 1/02/10

Olivier Sentieys 3

325

Évolutions technologiques

Year

Voltage [V]

Power per chip [W]

VDD current [A]

1998 2002 2006 2010 2014

0

0.5

1

1.5

2

2.5

0 0

200 500

Current

Power

Voltage

326

Évolutions technologiques

• Projections

– ... 2000 Watts, 3000 A !

– La surface de silicium doit donc rester constante pour rester autour de

100-200W et 300-500A

1

10

100

1000

10000

1985 1990 1995 2000 2005 2010

Power (Watts)

Vdd scaling

0,1

1

10

100

1000

10000

1985 1990 1995 2000 2005 2010

Icc (A)

386 486

Pentium

Pro

PII

PIV

Puissance Courant d'alimentation

Méthodologie de conception des circuits intégrés VLSI - 6. Faible consommation 1/02/10

Olivier Sentieys 4

327

2. Portabilité (1)

Em. Radio

Rec. Radio

Graphiques

Vidéo

Voix

Interface

• Multimédia

– Visioconférence H26x

– MPEGx,

• Interfaces

– Reconnaissance vocale

– Stylo inertiel

– Cryptage, authentification

• Mobilité

– UMTS, EDGE, GSM

– Internet Protocol

– Connexion réseaux locaux

2005 : mobilité et durée de vie

des batteries d'un agenda,

capacité multimédia d'un PC

328

Technologie des batteries

• Performances des

batteries

[P. Senn 2000]

250

200

150

100

50

0

100 200 300 400 Smaller

Lighter

Whr/l

Whr/kg

NiCd

NiMh

Lithium-Ion Liquid

Lithium-Ion Polymer

LTC Lithium-Ion Polymer

LTC Lithium-Alloy

Polymer

Technologies NiCd NiMh Li-ion Li-poly

Naissance

industrielle

1956 1990 1992 1996

Tension (V) 1.2 1.2 3.6 3.7

Epaisseur

(mm)

>6 >6 >6 3

Capacité

(Whr/kg)

30-50 60-90 70-140 115-140

Durée de vie

(cycles)

~1000 ~1000 500 500

• Exemple type

– 500 mAh Li-Pol = 1,7 Wh

• Exemple haute capacité

– 1400 mAh Li-Pol = 5 Wh

• >10 heures autonomie

– P < 400 mW

Méthodologie de conception des circuits intégrés VLSI - 6. Faible consommation 1/02/10

Olivier Sentieys 5

329

Terminal 3G Portable

Em. Radio

Rec. Radio

Graphiques

Vidéo

Voix

Interface

• Traitement

– 6-10 Milliards d'Instructions / sec

• Autonomie : 10h

• Poids : 500g (batteries)

500mW @ 6 GIPS

12 GIPS/W @ 6 GIPS

• Avec les processeurs actuels

– 30 Kg ou 10 minutes !!!

– ... avec quelques dizaines de DSP !!!

330

En conclusion (puissance)

• Evolution de la géométrie des transistors

– Densité de transistors augmente

– Fréquence d’horloge augmente

• La puissance des circuits augmente malgré

– la diminution de la tension d’alimentation

– l'amélioration des méthodes de conception

• Limitations ?

– Limites physiques

Chaleur : e.g. 100W sur 3 cm2

– Limites dépendantes de l’application

Ordinateurs portables, nomades (PDA)

Systèmes embarqués (ou enfouis)

Systèmes ultra basse-consommation

Commutateurs, stations de base en télécommunications, routeurs Internet, …

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

1

/

39

100%