Énoncé TP2 - Processeurs et caches

INF4170 – Architecture des ordinateurs

Hiver 2017 - TP2

Numéro 1 (50%) - Modification de processeurs

Modifiez les circuits de processeurs demandés afin d'y ajouter le support d'une nouvelle instruction.

Il s'agit d'une instruction permettant d'incrémenter une valeur directement en mémoire.

Voici les détails de l'instruction.

Nom : Memory Increment

Mnémonique : minc

Type d'instruction : Type-I

Champs :

•opcode : 0x6

•rs : registre contenant l'adresse mémoire de la valeur à incrémenter

•rt : n'est pas utilisé

•Imm : n'est pas utilisé

Exemple d'utilisation : minc $s3

Information : Le registre s3 contient une adresse mémoire. Cette adresse mène directement (sans

adressage indexé) à un mot en mémoire centrale. Il faut incrémenter la valeur et stocker le résultat

au même endroit en mémoire.

Expliquez ce qui est fait durant chacun des cycles de l'instruction minc et indiquez les valeurs des

bits de contrôle lors de chacun des cycles.

Vous devez modifier les processeurs suivants :

a) le processeur à un cycle (25%)

b) le processeur à pipeline sans gestion des aléas (25%)

Numéro 2 (50%) - Simulations de caches

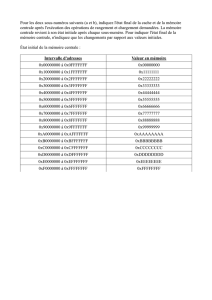

Pour les trois sous-numéros suivants (a, b, et c), indiquez l'état final du cache et de la mémoire

centrale après l'exécution des opérations de rangement et chargement demandées. La mémoire

centrale revient à son état initiale après chaque sous-numéro. Pour indiquer l'état final de la

mémoire centrale, n'indiquez que les changements par rapport aux valeurs initiales.

État initial de la mémoire centrale :

Intervalles d'adresses Valeur en mémoire

0x00000000 à 0x0FFFFFFF 0x00000000

0x10000000 à 0x1FFFFFFF 0x11111111

0x20000000 à 0x2FFFFFFF 0x22222222

0x30000000 à 0x3FFFFFFF 0x33333333

0x40000000 à 0x4FFFFFFF 0x44444444

0x50000000 à 0x5FFFFFFF 0x55555555

0x60000000 à 0x6FFFFFFF 0x66666666

0x70000000 à 0x7FFFFFFF 0x77777777

0x80000000 à 0x8FFFFFFF 0x88888888

0x90000000 à 0x9FFFFFFF 0x99999999

0xA0000000 à 0xAFFFFFFF 0xAAAAAAAA

0xB0000000 à 0xBFFFFFFF 0xBBBBBBBB

0xC0000000 à 0xCFFFFFFF 0xCCCCCCCC

0xD0000000 à 0xDFFFFFFF 0xDDDDDDDD

0xE0000000 à 0xEFFFFFFF 0xEEEEEEEE

0xF0000000 à 0xFFFFFFFF 0xFFFFFFFF

Voici les opérations à effectuer (ce sont les mêmes pour toutes les caches) :

Opération Adresse Valeur

LW 0x1934EDD8

LW 0x8944EFA4

SW 0xAF70ADC8 0x19887766

LW 0x0F58CC20

LW 0xBEADDEF0

SW 0x246EAF94 0xAF7F7FF1

LW 0x19060908

SW 0x876D247C 0x3003FFFF

SW 0x2823040C 0x1010FFAF

LW 0x33444444

LW 0x21448808

SW 0x0ACCBEDC 0x0ADD0001

LW 0x2144880C

SW 0x0ACCBED8 0xCAFECAFE

SW 0x2144880C 0xCCCCCCCC

LW 0x33444444

LW 0x2823040C

a) Première cache (20%)

Type de cache : set-associative cache

Taille d'un bloc : 4 mot

Nombre de bloc dans le cache : 8

Nombre d'ensemble : 2

Algorithme d'écriture dans le cache : write-through

Algorithme de sélection de bloc pour un index donné : Tant qu'il y a des blocs invalides dans

l'ensemble, on prend le premier bloc invalide de l'ensemble (de haut en bas), ensuite on utilise

l'algorithme LRU.

État initial du cache :

Index # du bloc

dans

l'ensemble

Étiquette 1er mot 2ème mot 3ème mot 4ème mot

0 0 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000

0 1 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000

0 2 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000

0 3 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000

1 0 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000

1 1 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000

1 2 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000

1 3 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000

b) Deuxième cache (15%)

Type de cache : fully-associative cache

Taille d'un bloc : 2 mots

Nombre de blocs dans le cache : 8

Algorithme d'écriture : write-back

Algorithme de sélection de bloc : Tant qu'il y a des blocs invalides, on prend le premier bloc

invalide (de haut en bas), ensuite on utilise l'algorithme LRU.

État initial du cache :

Validité Saleté Adresse du bloc Premier mot Deuxième mot

0 0 0x00000000 0x00000000 0x00000000

0 0 0x00000000 0x00000000 0x00000000

0 0 0x00000000 0x00000000 0x00000000

0 0 0x00000000 0x00000000 0x00000000

0 0 0x00000000 0x00000000 0x00000000

0 0 0x00000000 0x00000000 0x00000000

0 0 0x00000000 0x00000000 0x00000000

0 0 0x00000000 0x00000000 0x00000000

c) Troisième cache (15%)

Type de cache : direct-mapped cache

Taille d'un bloc : 2 mots

Nombre de blocs dans le cache : 4

Algorithme d'écriture : write-through

État initial du cache :

Index Validité Étiquette Premier mot Deuxième mot

00 0 0x0000000 0x00000000 0x00000000

01 0 0x0000000 0x00000000 0x00000000

10 0 0x0000000 0x00000000 0x00000000

11 0 0x0000000 0x00000000 0x00000000

Remise

Le travail peut être fait seul ou en équipe de 2 personnes. Le travail doit être remis dans un

document PDF nommé selon les codes permanents des auteurs. Le document doit être remis par

Moodle avant le 21 avril 2017 à 13h30 (groupe 50). Aucun retard ne sera accepté et une pénalité

sera appliquée pour un documet non conforme sans les codes permanents.

1

/

5

100%