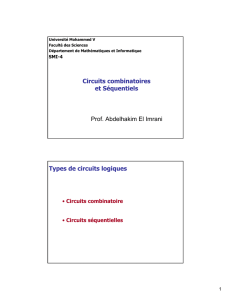

Circuits sequentiels

1

Pour pivoter horizontalement ou

verticalement un symbole, cliquez

dessus avec le bouton droit de la

souris et choisissez « Flip

Horizontal » ou « Flip Vertical ».

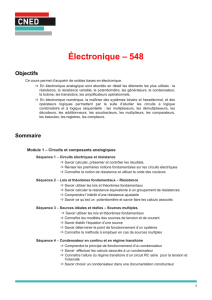

IUT La Rochelle - Dépt R&T 2009-2010

Info 1ème année – Module I2 Laurent Demay

Circuits séquentiels T. Dumartin, P. Coulaud

T.P. n°3 : Circuits séquentiels

Nous allons réaliser aujourd’hui des circuits séquentiels. La sortie d’un circuit séquentiel ne sera pas uniquement fonction des

entrées en instantané, mais également des états précédents d’entrées ou de sorties. Nous avons besoin de réaliser des fonctions

de mémorisation de certaines données, et ceci se fera à l’aide de bascules.

1. Diviseur de fréquence

Nous allons utiliser le modèle de bascule D disponible dans le logiciel Quartus pour réaliser un diviseur de fréquence vu au TD n°3

Créez dans un nouveau dossier TP3 un projet appelé circuits_seq composé du schéma div_freq.bdf suivant

La bascule D correspond au symbole dff de la librairie « C:/altera/91/quartus/librairies/primitives/storage » .

Mettez un niveau logique haut « ../primitives/others/vcc » sur les entrées PRN et CLRN, car les fonctions Preset

(mise de la sortie à ‘1’) et Clear (mise de la sortie à ‘0’) sont actives à l’état bas.

Sélectionnez comme en entité principale, compiler puis simulez le circuit en mettant en entrée un signal d’horloge de 50 MHz.

Mesurez le temps de propagation de la bascule (délai entre le front actif du signal d'horloge et le changement sur les sorties)

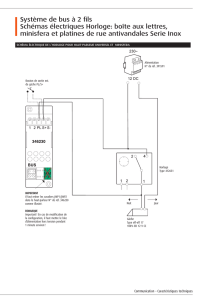

La carte DE2 dispose de deux horloges à 27 MHz et à 50 MHz. Nous voudrions pouvoir disposer d’une horloge de très basse

fréquence (de l’ordre de 1 Hz) pour avoir le temps d’examiner l’évolution de nos circuits séquentiels.

Combien faut-il de circuits « diviseurs par 2 de fréquence » en série pour obtenir en sortie un signal d’horloge d’environ

1,49 Hz à partir d’un signal d’horloge en entrée de 50 MHz ?

Modifiez div_freq.bdf en dupliquant le diviseur par 2 de fréquence par copier/coller pour créer le circuit voulu.

Affectez les broches pour utiliser l’horloge à 50 Mhz CLOCK_50 en entrée et la diode rouge LEDR[0] en sortie.

Compilez le schéma, et programmez-le sur la carte DE2 et testez. Quelle est la période de clignotement de la diode ?

Créez un Symbol File que vous appellerez div_freq.bsf à partir de ce schéma.

2

2. Circuit « Shift Register »

Ajoutez un nouveau « Bloc Diagram/Schematic File » nommé shift_reg.bdf au projet circuits_seq

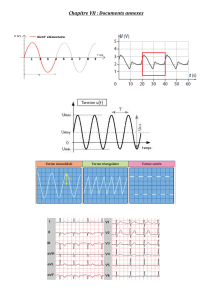

Réaliser le circuit suivant, où H est l’horloge qui cadence l’évolution des bascules D, E la donnée à l’entrée du circuit,

et S[2..0] la sortie (sur 3 bits) du circuit.

Faites de ce schéma l’entité principale du projet en sélectionnant « Project / Set As Top-Level Entity… »

Simuler le circuit avec des signaux semblables à ceux ci-dessous, et en déduire la fonction logique réalisée par ce montage.

Donnez des exemples d'utilisation de ce type de circuit (recherchez sur Internet).

3. Circuit « compteur binaire modulo 4 synchrone »

Un compteur synchrone est un compteur dont tous les étages (bascules) sont commandés par le même signal d'horloge.

Ce mode de fonctionnement permet de limiter la durée des périodes d'instabilité et par conséquent autorise des vitesses plus élevées

qu'en mode asynchrone.

Un compteur modulo 4 fait évoluer sa sortie Q1Q0 à chaque

front montant (ou descendant) d’horloge de la façon suivante :

0 1 2 3 0 1 …, soit en binaire :

00 01 10 11 00 01 …

Un compteur modulo 4 voit sa sortie (codée donc sur 2 bits)

évoluer selon la table de vérité ci-contre :

Pour mémoriser l’état du compteur (codé sur 2 bits), nous

allons utiliser 2 bascules D pour jouer le rôle de case mémoire.

Les données correspondant à l’état suivant sont en fait les

niveaux à placer en entrée des bascules D, afin que ces niveaux

soient transmis en sortie lors du front d’horloge suivant, selon le

principe représenté ci-contre.

Ajoutez un nouveau « Bloc Diagram/Schematic File »

nommé compteur.bdf au projet circuits_seq

A partir de la table de vérité, donnez les expressions des

signaux n+1

1

Q et n+1

0

Q à générer à partir de n

1

Q et

n

0

Q

.

Réalisez le circuit en utilisant deux bascules D, une entrée pour l’horloge et le module div_freq, deux sorties pour les bits

du compteur et les portes logiques nécessaires.

Affectez les broches pour utiliser l’horloge à 50 Mhz et deux leds en sortie pour le compteur.

Sélectionnez le schéma comme en entité principale, puis compilez.

Programmez-le sur la carte DE2 et vérifiez le fonctionnement.

Etat présent Etat suivant

H

n

1

Q

n

0

Q

n+1

1

Q n+1

0

Q

0 0 0 1

0 1 1 0

1 0 1 1

1 1 0 0

Q

/Q

D

Q

/

Q

D Q

/

Q

D

S0

S

1

S

2

E

H

t

H

E

Cases mémoire

(

basc. D

)

D

Q

H

D

Q

Circuit combinatoire

(génération des états suivants

à

p

artir des états

p

résents

)

?

n

+1

0

Q

n

+1

1

Q

n

0

Q

n

1

Q

1

/

2

100%