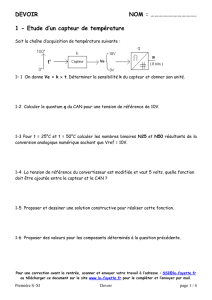

Capteur intégré tactile d`empreintes digitales à microstructures piezoré

INSTITUT NATIONAL POLYTECHNIQUE DE GRENOBLE

N° attribué par la bibliothèque

|__/__/__/__/__/__/__/__/__/__/

THESE

pour obtenir le grade de

DOCTEUR DE L'INPG

Spécialité : MICROELECTRONIQUE

préparée au laboratoire TIMA

Dans le cadre de l'Ecole Doctorale

ELECTRONIQUE, ELECTROTECHNIQUE, AUTOMATIQUE, TELECOMMUNICATION,

SIGNAL

présentée et soutenue publiquement

par

Fabien PARRAIN

le 02 décembre 2002

Titre :

Capteur intégré tactile d'empreintes digitales à microstructures piezorésistives

________

Directeur de thèse :

Docteur Bernard COURTOIS

________

JURY

M. Christian SHAEFFER , Président

M. Tarik BOUROUINA , Rapporteur

M. Dominique COLLARD , Rapporteur

M. Bernard COURTOIS , Directeur de thèse

M. Benoît CHARLOT , Co-encadrant

M. Alain BOSSEBOEUF , Examinateur

Remerciements

__________________________________________________________________________________________

1

REMERCIEMENTS :

Je tiens, avant tout, à remercier M. Bernard COURTOIS, le directeur du laboratoire TIMA et

du CMP, pour m'avoir accueilli au sein du groupe Microsystème (groupe MCS récemment rebaptisé

MNS pour Micro et Nano Systèmes) et pour m'avoir fourni tous les moyens nécessaires au bon

déroulement de cette thèse de doctorat.

Je remercie particulièrement M. Benoît CHARLOT avec qui j'ai étroitement collaboré durant les trois

années passées au sein du laboratoire TIMA, ainsi que M. Salvador MIR qui a guidé mes premiers pas

en conception analogique intégrée.

Je remercie M. Hubert DELORI pour son éternelle bonne humeur ainsi que M. Alexandre

CHAGOYA, ingénieur système au CIME, qui est certainement l'homme le plus serviable qui m'a été

donné de rencontrer jusqu'à ce jour.

Je remercie les membres de mon jury, M. Tarik BOUROUINA et M. Dominique COLLARD pour

avoir consacré une partie de leur temps afin de juger mon travail, M. Christian SCHAEFFER pour

avoir accepter de présider ma thèse et M. Alain BOSSEBOEUF pour m'avoir fait l'honneur d'y

participer.

Je remercie chaleureusement tous les actuels ou anciens membres du groupe Microsystème : Zein,

Skandar, Libor, Slava, et plus particulièrement ceux du fameux bureau 120 : Damien, Sergio, Nicolas,

Guillaume ainsi que l'inévitable Christian.

Un grand merci à l'équipe du CMP et plus particulièrement à M. Kholdoun TORKI ainsi qu'à M. Jean-

François PAILLOTIN qui a été obligé de fermer les yeux sur de si nombreuses erreurs de DRC …

Je remercie aussi l'équipe administrative du TIMA et plus particulièrement Isabelle (elle se

reconnaîtra …) ainsi que Chantal pour leur gentillesse et leur serviabilité.

Enfin, je remercie Isabelle pour avoir supporté toutes ces années durant lesquelles je me suis exilé loin

d'elle.

Table des matières

__________________________________________________________________________________________

3

TABLE DES MATIERES :

Chapitre I : Introduction.......................................................................................................13

I.1 Les microsystèmes.................................................................................................................13

I.2 Marché des microsystèmes....................................................................................................14

I.3 Structure du mémoire de thèse ..............................................................................................14

Chapitre II : Etat de l'art ...................................................................................................... 17

II.1 Introduction ...........................................................................................................................17

II.2 La biométrie comme méthode d'identification ......................................................................17

II.3 L’empreinte digitale ..............................................................................................................19

II.3.1 Caractéristiques d’une empreinte digitale........................................................................19

II.3.2 Méthode d’extraction de la signature et de reconnaissance de l’empreinte digitale........20

II.4 Les capteurs d’empreintes digitales.......................................................................................22

II.4.1 Les capteurs d'empreintes digitales macroscopiques .......................................................22

II.4.2 Les capteurs intégrés d'empreintes digitales ....................................................................24

II.5 Conclusion.............................................................................................................................31

Chapitre III : Conception et réalisation............................................................................... 33

III.1 Introduction ...........................................................................................................................33

III.2 Capteur tactile réalisé par micro-usinage en volume.............................................................33

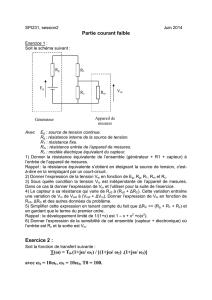

III.2.1 Principe de fonctionnement du capteur .......................................................................34

III.2.2 Cahier des charges .......................................................................................................35

III.3 La piezorésistivité..................................................................................................................36

III.3.1 La piezorésistivité dans le cas du silicium monocristallin...........................................36

III.3.2 Facteurs de jauge .........................................................................................................39

III.3.3 Récapitulatif concernant les facteurs de jauge.............................................................42

III.3.4 Explication physique du phénomène ...........................................................................42

III.3.5 Piezorésistivité du silicium polycristallin....................................................................44

III.3.6 Conclusion sur la piezorésistivité ................................................................................45

III.4 Le micro-usinage en volume .................................................................................................45

III.4.1 La gravure anisotrope du silicium : généralités...........................................................46

III.4.2 Le micro-usinage en volume par la face avant ............................................................50

III.4.3 Le micro-usinage en volume par la face arrière .......................................................... 52

III.4.4 Le micro-usinage en volume mixte par la face avant et arrière...................................53

III.4.5 Le micro-usinage électrochimique ..............................................................................53

III.4.6 Détermination des temps de gravure : Calculs et simulations .....................................54

III.4.7 Conclusion sur le micro-usinage en volume................................................................ 58

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

61

61

62

62

63

63

64

64

65

65

66

66

67

67

68

68

69

69

70

70

71

71

72

72

73

73

74

74

75

75

76

76

77

77

78

78

79

79

80

80

81

81

82

82

83

83

84

84

85

85

86

86

87

87

88

88

89

89

90

90

91

91

92

92

93

93

94

94

95

95

96

96

97

97

98

98

99

99

100

100

101

101

102

102

103

103

104

104

105

105

106

106

107

107

108

108

109

109

110

110

111

111

112

112

113

113

114

114

115

115

116

116

117

117

118

118

119

119

120

120

121

121

122

122

123

123

124

124

125

125

126

126

127

127

128

128

129

129

130

130

131

131

132

132

133

133

134

134

135

135

136

136

137

137

138

138

139

139

140

140

141

141

142

142

143

143

144

144

145

145

146

146

147

147

148

148

149

149

150

150

151

151

152

152

153

153

154

154

155

155

156

156

157

157

158

158

159

159

160

160

161

161

162

162

1

/

162

100%