XII- INTRODUCTION AU MICROCONTRÔLEUR M68HC12

XII- INTRODUCTION AU MICROCONTRÔLEUR

M68HC12

12.1- La notion de Microcontrôleur

L’objectif d’un microcontrôleur est de :

¢ Diminuer les interconnexions de circuits, sources de plus-values et de pannes.

¢ Intégrer sur la même puce de silicium le microprocesseur et un certain nombre de périphériques.

Parmi les périphériques que l’on va intégrer on trouve :

- La mémoire RAM

- La mémoire ROM.

- La mémoire EEPROM

- Des ports de liaisons parallèles

- Des ports de liaison série

- Des compteurs temporisateurs

- Des convertisseurs numériques analogiques et analog/ numériques

- Des contrôleurs de DMA et d’interruption

Etc...

Remarque : Le microcontrôleur universel n’existe pas

12.2 Introduction au 68HC12

• circuit intégré HCMOS

• CPU avec registres et ALU

• Mémoires (RAM, EEPROM, Flash)

• Timer

• Divers organes d’entrée/sortie

• Convertisseur A/D

12.3 Deux versions du M68HC12

Comparaison MC68HC812A4 MC68HC912B32

E/S Série

Modulation de la largeur

d’impulsion

Extension de mémoire

Application

Mémoire

2 ports série asynchrone (SCI)

Un port série synchrone (SPI)

Non

Jusqu’à 5 Mbytes

Applications nécessitant de

l’extension mémoire

1 Kbyte RAM

4 Kbytes EEPROM

Un port série asynchrone (SCI)

Un port série synchrone (SPI)

Un contrôleur supplémentaire de

transmission série

4 canaux 8-bit

non

Application demandant de multiples

ports d’E/S

1 Kbyte RAM

768 bytes EEPROM

32 Kbytes FLASH EEPROM

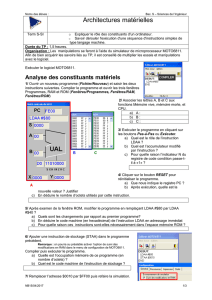

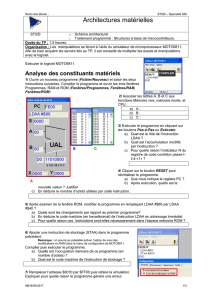

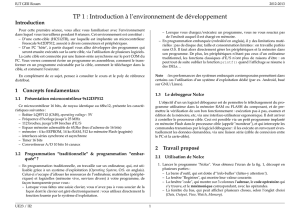

12.4 Les registres

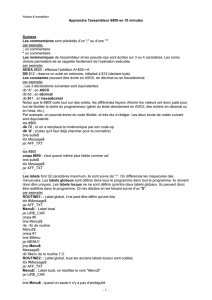

12.5 Le plan mémoire

Le 68HC12 est un microcontrôleur 16-bits, 16 bits données, 16 bits adresses

possibilité d'adresser 216 positions en mémoire

=64 Kbytes de 0000h à FFFFh

Il peut utiliser des mémoires 8-bits

Gamme des adresses Usage Description

$0000 - $01FF Registres de la CPU On chip

$0800 - $09FF

$0A00 - $0BFF Code/donnée utilisateur

Réservé pour D-bug12 1 Kbyte

RAM On chip

$0D00 - $0FFF Code/donnée utilisateur 768 byte on-chip EEPROM

$8000 - $F67F

$F680 - $F6BF

$F6C0 - $F6FF

$F700 - $F77F

$F780 - $F7FF

$F800 - $FBFF

$FC00 - $FFBF

$FFC0 - $FFFF

Code D-Bug12

Fonctions accessibles à l'utilisateur

Données D-Bug12

Code départ D-Bug12

Table des sauts d'interruption

Réservé pour le boot (extension)

Boot EEPROM

Reset vecteur interruption

32 Kbytes on-chip

EEPROM FLASH

Accum. A 7 Accum. B 0

15 Double Accumulateur D 0

Registre Index X

Registre Index Y

Pointeur de PILE

Compteur Ordinal

S X H I N Z V C

Retenue

Dépassement

Zéro

Négatif

Masque inter.

Retenue Aux.

Masque inter.

Stop

Registre Conditions

12.6 Les modes d'adressage

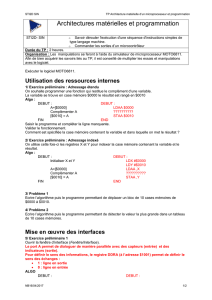

il y a plusieurs manières d'accéder à des données ou à des codes stockés dans une cellule mémoire:

"modes d'adressage"

Modes d'adressage du 68HC12

1. Immédiat

2. Direct

3. Etendu

4. Indexé (pré et post incrément et décrément)

5. Indexé indirect

6. Inhérent

7. Relatif

¢ Adressage immédiat

La donnée suit immédiatement l'instruction.

# signifie adressage immédiat

Exemple

ldda #!64 ; décimal 64 dans A

ldda #$64 ; hex 64 dans A

ldx #$1234 ; hex 1234 dans X

¢ Adressage direct

Adressage page zéro 256 emplacement mémoire 00h à FFh (adresse 8-bits) LSByte

La CPU met le MSByte à 00h On peut adresser donc de 0000h à 00FFh (256 emplacements)

Exemple:

ldaa $64 ; ($0064) dans A

Stab !255 ; B dans ($00FF)

ldx !10 ; ($000A:000B) dans X

¢ Adressage étendu

On utilise l'adresse sur 16-bit pour adresser 216 emplacements mémoire C'est une instruction 3-bytes,

l'adresse est sur les deux bytes juste après l'opcode.

Exemple:

ldaa $1234 ; ($1234) dans A

ldd $1234 ; ($1234:1235) dans D

stx $c000 ; X dans ($C000:C001)

¢ Adressage indexé

Il fait intervenir les registres index X et Y et des fois SP et PC .

Format : Operation Offset, registre_index

Registre_index : X, Y, SP ou PC

offset 5, 9, ou 16 bits valeur ajoutée au contenu du registre_index

1er cas: offset=constante:

Exemple:

ldaa ,x ; (x + 0) 5 bit offset dans A

ldaa 0,x ; (x + 0) 5 bit offset dans A

ldaa -!64,Y ; (Y-64) 9 bit offset dans A

Staa -1, SP ; A dans (SP – 1) 5 bit offset

ldaa !5000,PC ; (PC + 5000) 16 bit offset dans A

2ème cas Index avec incrément et décrément (pré et post):

Le format est le suivant :

Opération valeur, - registre_index pré décrémentation

Opération valeur, registre_index- post décrémentation

Opération valeur, +registre_index pré incrémentation

Opération valeur, registre_index+ post incrémentation

La valeur est ajoutée ou soustraite du registre index avant (pré) ou après (post) que la donnée soit

transférée.

Valeur : entier 1 to 8

Registre_index: X, Y ou SP

Exemple:

ldaa !7, -X ; X-7 dans X, (X) dans A pré décrémentation

ldaa !2, X+ ; (X) dans A, X+2 dans X post incrémentation

3ème cas : Accumulateur offset

Format de l'instruction:

Opération Registre, registre_index

register: A, B, ou D

register_index : X, Y, SP, PC

L'instruction calcule l'adresse effective en ajoutant 8 ou 16 bits au registre index. Ceci ne change pas la

valeur actuelle du registre.

Exemple:

ldaa B,X ; (X+B) dans A

ldab A,Y ; (Y+A) dans B

ldy D,X ; (X+D:X+D+1) dans Y

4ème cas : Indexé indirect

Ce mode est indirect car on va chercher de l'adresse de la donnée qui elle sera utilisée pour aller

chercher la donnée.

Exemple

ldx #$5000 ; $5000 dans X (on initialise X)

ldaa [$64,X] ; ((5064)) dans A

ou bien

staa [-1,X] ; A dans (($4FFF))

¢ Adressage inhérent

L'instruction elle-même contient l'adresse où se trouve la donnée.

Exemple:

Aba ; A+B dans A

Inx ; X+1 dans X

¢ Adressage relatif

Si on dispose d'une mémoire organisée en pages, il suffit d'indiquer l'adresse à l'intérieur de la page et

de garder l'adresse de la page dans un registre (registre des pages).

Adresse effective AE = base B + dépassement D (D est assez grand)

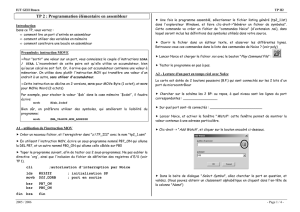

12.7 Programmation en assembleur du M68HC12

12.7.1 Exemple LDX $F682 0800 FE F6 82

JSR 0,X 0803 15 00

PSHA 0805 36

LDAA #$3D 0806 86 3D

12.7.2 Syntaxe de l'assembleur

Un programme est spécifique d'un microprocesseur

Une instruction 4 champs

Champs du code source

Label (étiquette) Opcode Opérande Commentaire

Exemple: LDX $F682 ; Faire appel à getchar

a- champ label ou étiquette ( 16 caractères : )

b- champ opération (code d'instruction)

c- champ opérande (soit l'opérande ou son adresse)

d- champ commentaires (commence par ; )

Remarque

Labels interdits 612FG :

Début

LDAB :

12.7.3 Le jeu d'instruction du M68HC12 (voir document PDF, notes de cours)

Exemple:

Retard: equ !100

$MACRO delay_100

PSHA ; sauvegarder le contenu de A

LDAA #retard

Loop: DECA

BNE loop

PULA ; récupérer le contenu de A

$MACROEND

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

1

/

15

100%