Exercices GPA770

GPA770 Microélectronique appliquée

Exercices – série B.1

1. Considérez le segment de code suivant. Quelles instructions de branchement seront

activées à la suite de l’exécution du code suivant? Répondez oui ou non pour chaque

instruction.

LDAB #2

SUBB #$DF

…suite aux deux instructions, B = $02 - $DF = $23, avec

N=0, Z=0, V=0 et C=1, donc:

a) BEQ non d) BMI non

b) BLO oui e) BHI non

c) BGT oui f) BRA oui

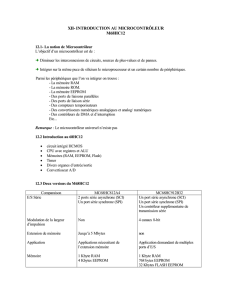

2. Un instruction en mode d’adressage direct (DIR) peut seulement accéder des données

dans une étendue d’adresses de 0000 à 00FF. Est-ce vrai que l’instruction doit aussi

être dans cette étendue d’adresses?

Non, l’instruction peut être à n’importe quel endroit dans toute la mémoire.

3. Quel est le seul mode d’adressage d’une instruction qui ne forme pas une adresse

mémoire?

Le mode d’adressage inhérent (INH).

4. Quelle adresse mémoire sera accédée par le CPU pour les exemples suivants

d’adressage indexé, sachant que l’index X pointe à l’adresse mémoire $0800:

a) LDAA 2, X addresse : $0802

b) STAA 2, +X addresse : $0802

c) LDAA -2, X addresse : $07FE

4. Donnez 2 instructions qui indiquent s’il y a eu emprunt en affectant le bit d’état C du

CCR.

La plupart des instructions qui effectuent un soustraction, e.g., SUBA, SBS, SBCB,

SUBD, et CMPA., indiquent s’il y a eu emprunt avec le bit C.

5. Est-ce que les bits N et Z du CCR peuvent les deux être égal à 0, ou bien à 1, suite à

l’exécution d’une instruction LDAA?

A la suite d’un LDAA, les bits N et Z ne peuvent les deux être ‘1’, mais peuvent les

deux être ‘0’.

6. Supposez qu’on veut exécuter (d’une façon indépendante) le segment de code suivant

avec le 68HC12. Quelle sera la valeur des bits d’état C, N, V et Z au registre CCR, ainsi

que le contenu de l’accumulateur A, juste après l’exécution de la séquence de code?

LDAA #$95

ADDA #$12

ADCA #%01011001

A = $00, Z = 1, C = 1, V = 0, N = 0

7. Écrire une séquence d’instructions qui incrémente un nombre qui est représenté sur 2

octets (16 bits) en mémoire, sans devoir utiliser les accumulateurs A et B.

Voir l’exemple codé exB1_8 pour le code assembleur.

RAMStart EQU $0800

ROMStart EQU $4000

ORG RAMStart

NUM_DATA FDB $05FF ;exemple de valeur à incrémenter

ORG ROMStart

LDX #RAMStart

INC 1,X

BNE DONE

INC 0,X

DONE END

8. Quel est le rôle d’un assembleur?

La conversion de fichiers source (qui sont écrits en langage assembleur) en code

machine comprit par le CPU.

7. Supposez que le registre IY contient $C919, et que le registre SP contient $1000. Quel

sera l’impact sur le contenu de IY, de SP, et de la mémoire RAM juste après l’exécution

de l’instruction PSHY?

IY =

SP =

8. Assemblez ce code assembleur à la main, et organiser le code machine résultant dans

la table qui suit. Il s’agit de montrer les valeurs numériques hexadécimales

correspondant aux adresses mémoire après que ce programme a été assemblé. Combien

d’octets le programme principal occupe t-il en mémoire ROM?

ORG $C010

RMB $10

AGAIN BRCLR 3, X+, $F0, AGAIN

Adresse mémoire

Valeur numérique (hex)

C020

0F

C021

32

C022

F0

C023

FC

9. Assemblez le segment de code assembleur suivant à la main, et organiser le code

machine dans la table qui suit.

ORG $1000

Var FCB $50

ORG $2000

LDAA Var

Loop INCB

SUBA #5

STAA Var

BEQ Loop

END

Adresse mémoire

Valeur

1000

50

…

…

2000

B6

10

00

2003

52

2004

80

05

2006

7A

10

00

2009

27

F8

10. Est-ce qu’on peut initialise un pointeur de pile SP avec l’adresse de la première

instruction du programme?

Oui. En fait, on initialise souvent de cette façon car les programmes grandissent

vers le bas, tandis que la pile grandit vers le haut.

11. Supposez que le registre IY contient $C919, et que le registre SP contient $1000.

Quel sera l’impact sur le contenu de IY, de SP, et de la mémoire RAM juste après

l’exécution de l’instruction PSHY?

IY = $C919

SP = $0FFE

12. Écrivez un programme qui compte le nombre de bytes dans une table qui sont égal à

zéro. La table consiste de 6 nombres et commence à l’adresse $2000. Stocker les

résultats à l’adresse mémoire $5000.

Result EQU $5000

Table EQU $2000

ORG $1100

CNT FCB $06

ORG $1000

LDAA CNT

LDX #Table

LDY #$0000

TEST CMPA #$00

BEQ DONE

LDAB 1,X+

Adresse mémoire

Valeur numérique

$0FFE

$C9

$0FFF

$19

$1000

BNE Next

INY

Next DECA

BRA TEST

DONE STY Result

END

13. Quel est le contenu du registre d’index IX après l’exécution du programme suivant:

LDS #$2000

PSHA

PSHY

TSX

PULX

[IX] = [IY]

14. En partant du programme suivant:

ORG $F054

LDS #$7F88

LDY #$AB63

LDAB #$36

ABY

PSHY

SUBB #$2A

a) Quel est le contenu des registres clés du 68HC12 après l'exécution du programme?

B = $0C

Y = $AB99

SP = $7F86

PC = $F061

CCR: N = 0, Z = 0

b) Quels sont les parties du CCR qui sont modifiées d’après l’exécution de PSHY et

quels sont leurs nouveaux contenus?

Aucunes sont modifiées

6

6

7

7

8

8

9

9

10

10

11

11

12

12

1

/

12

100%