Rapport

Rapport de projet

Traitement vidéo

Sommaire

Présentation..................................................................................................................................4

Cahier des charges.........................................................................................................................5

Choix des composants....................................................................................................................5

Organisation..................................................................................................................................8

Le projet........................................................................................................................................9

La mémoire ...............................................................................................................................9

RS232......................................................................................................................................11

Présentation de la caméra........................................................................................................12

Récupération des données.......................................................................................................13

Traitement sur les données......................................................................................................17

Le programme .........................................................................................................................19

Connexion entre la caméra et la carte FPGA ..............................................................................21

Etat actuel du projet....................................................................................................................22

Conclusion...................................................................................................................................22

Présentation

Dans ce rapport, nous allons voir quels étaient les objectifs du projet qui ont été fixé, son

environnement et ses étapes pour sa réalisation.

Ainsi, l’objectif de ce projet est de permettre au robot PROMOCO de suivre, de façon autonome, une

ligne tracée sur le sol et de changer son comportement selon la courbe de la ligne ou encore selon

les formes autour de cette ligne. Par exemple, si le robot détecte un carré de couleur rouge, il devra

s’arrêter. Pour cela, il faut définir quel sera le système adapté pour acquérir des images, et appliquer

des algorithmes sur ces captures pour reconnaitre la ligne ou les formes sur le sol. Ceci défini les

objectifs de ce projet.

Voici un exemple montrant une application concrète de ce projet :

Enfin, pour le traitement 3, on peut imaginer que si un rond vert est relevé, le robot devra ralentir

son allure.

Cahier des charges

Pour parvenir à ce système, l’objectif est de s’assurer que les composants qui traiteront les images

puissent être performants tout en étant évolutifs pour d’éventuels futurs algorithmes.

Le principe sera d’obtenir une image et de l’afficher sur un écran pour observer le résultat de

l’acquisition et l’effet des traitements sur cette image.

Ce système devra au moins posséder :

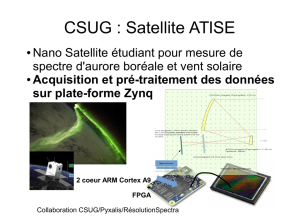

- Un ARM

- Un FPGA

- Une caméra

La caméra sera chargée bien entendu de capturer un flux d’image et devra être configurée pour

fournir les données sur 8 bits sous le format RGB qui est le plus facile à gérer.

Le processeur ARM aura la charge de configurer la caméra à travers le protocole I2C et devra

également afficher l’image reçu sur un écran TFT/LCD.

Enfin, le FPGA aura pour rôle de récupérer l’image fourni par la caméra, d’appliquer les divers

algorithmes sur l’image reçu et d’envoyer le résultat vers le ARM via une liaison série.

On en déduit le schéma fonctionnel suivant :

Caméra

I2C

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

1

/

23

100%